REFERENCE DESIGN PMC - 2002050 PMC PMC-Sierra, Inc.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

# PM7341, PM8316

# S/UNI-IMA-84, TEMUX-84

# S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

PRELIMINARY ISSUE 2: JUNE 2001

REFERENCE DESIGN PMC - 2002050 PMC-Sierra, Inc.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## PUBLIC REVISION HISTORY

| lssue<br>No. | Issue Date       | Details of Change                        |

|--------------|------------------|------------------------------------------|

| 2            | June 2001        | Updated Schematics                       |

|              |                  | Added Board Modifications section        |

|              |                  | Modified Software Interface section      |

|              |                  | Inclusion of Bill of Materials           |

|              |                  | Inclusion of Layout                      |

|              |                  | Inclusion of VHDL code                   |

|              |                  | Updated SEEP register values             |

|              |                  | Minor grammatical and formatting changes |

| 1            | December<br>2000 | Document Created.                        |

REFERENCE DESIGN PMC - 2002050 PMC-Sierra, Inc.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## **CONTENTS**

| 1 | INTF | RODUCTION 1                                                 |

|---|------|-------------------------------------------------------------|

|   | 1.1  | PURPOSE1                                                    |

|   | 1.2  | SCOPE1                                                      |

|   | 1.3  | APPLICATIONS 1                                              |

|   |      | 1.3.1 ATM EDGE SWITCH IMA AND UNI PORT CARD 1               |

|   |      | 1.1.1 ATM MULTISERVICE SWITCH, ANY SERVICE ANY PORT<br>CARD |

| 2 | FEA  | TURES                                                       |

| 3 | FUN  | CTIONAL DESCRIPTION                                         |

|   | 3.1  | DATA FLOW 4                                                 |

|   |      | 3.1.1 TRANSMIT DIRECTION                                    |

|   |      | 3.1.2 RECEIVE DIRECTION                                     |

| 4 | BLO  | CK DESCRIPTION                                              |

|   | 4.1  | OPTICS                                                      |

|   | 4.2  | PM5342 SPECTRA-155 13                                       |

|   | 4.3  | PM8316 TEMUX-84 13                                          |

|   | 4.4  | PM7341 S/UNI-IMA-8413                                       |

|   |      | 4.4.1 SDRAM 14                                              |

|   | 4.5  | PM7350 S/UNI-DUPLEX 14                                      |

|   | 4.6  | BUS INTERFACES 14                                           |

|   |      | 4.6.1 TELECOM BUS INTERFACE                                 |

|   |      | 4.6.2 SBI BUS INTERFACE 16                                  |

|   |      | 4.6.3 UTOPIA LEVEL 2 BUS INTERFACE                          |

| REFERENCE DESIG<br>PMC - 2002050 | N    | ISSUE 2                                                 | S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT |

|----------------------------------|------|---------------------------------------------------------|---------------------------------------|

|                                  | 4.7  | COMPACTPCI BRIDGE                                       | 17                                    |

|                                  | 4.8  | SEEP                                                    |                                       |

|                                  |      | 4.8.1 CARD ID NUMBER                                    |                                       |

|                                  |      | 4.8.2 SERIAL EEPROM LOAD RE                             | EGISTERS 19                           |

|                                  | 4.9  | CPLD                                                    |                                       |

|                                  |      | 4.9.1 LOCAL BUS GLUE LOGIC                              |                                       |

|                                  | 4.10 | FULL HOT SWAP CAPABILITY                                |                                       |

|                                  |      | 4.10.1 POWER SUPPLY WITH HO                             | T SWAP CONTROLLER 24                  |

|                                  |      | 4.10.2 EJECTOR HANDLE AND LE                            | ED 25                                 |

|                                  | 4.11 | CPCI BRIDGE HARDWARE INTER                              | RFACES 26                             |

|                                  |      | 4.11.1 CPCI SYSTEM BUS INTERI                           | FACE 26                               |

|                                  |      | 4.11.2 PCI 9030-LOCAL BUS INTE                          | RFACE 26                              |

|                                  | 4.12 | OSCILLATORS                                             |                                       |

| 5                                | ANAL | YSIS                                                    |                                       |

|                                  | 5.1  | INTERFACE TIMING                                        |                                       |

|                                  |      | 5.1.1 SPECTRA-155 – TEMUX-84                            | TELECOM DROP BUS 29                   |

|                                  |      | 5.1.2 SPECTRA-155 – TEMUX-84                            | TELECOM ADD BUS 30                    |

|                                  |      | 5.1.3 TEMUX-84 – S/UNI-IMA-84                           | SBI ADD BUS INTERFACE . 32            |

|                                  |      | 5.1.4 TEMUX-84 – S/UNI-IMA-84                           | SBI DROP BUS INTERFACE33              |

|                                  |      | 5.1.5 S/UNI-IMA-84 – S/UNI-DUP<br>TRANSMIT BUS INTERFAC | LEX UTOPIA LEVEL 2<br>E               |

|                                  |      | 5.1.6 S/UNI-IMA-84 – S/UNI-DUP<br>RECEIVE BUS INTERFACE | LEX UTOPIA LEVEL 2<br>                |

|                                  |      | 5.1.7 PCI 9030 TIMING DIAGRAM                           | /IS 41                                |

|                                  | 5.2  | SIGNAL INTEGRITY SIMULATION                             | S 53                                  |

REFERENCE DESIGN

| REFERENCE DESIC<br>PMC - 2002050 | ЗN   |        | ISSUE 2               | S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT |

|----------------------------------|------|--------|-----------------------|---------------------------------------|

|                                  |      | 5.2.1  | PRE-LAYOUT            |                                       |

|                                  |      | 5.2.2  | TELECOM BUS           |                                       |

|                                  |      | 5.2.3  | SBI BUS               |                                       |

|                                  |      | 5.2.4  | UTOPIA L2 BUS         |                                       |

|                                  |      | 5.2.5  | PCI 9030 INTERFACE    |                                       |

|                                  | 5.3  | POW    | ER ESTIMATE AND THE   | ERMAL ANALYSIS 60                     |

| 6                                | DESI | GN ISS | SUES                  |                                       |

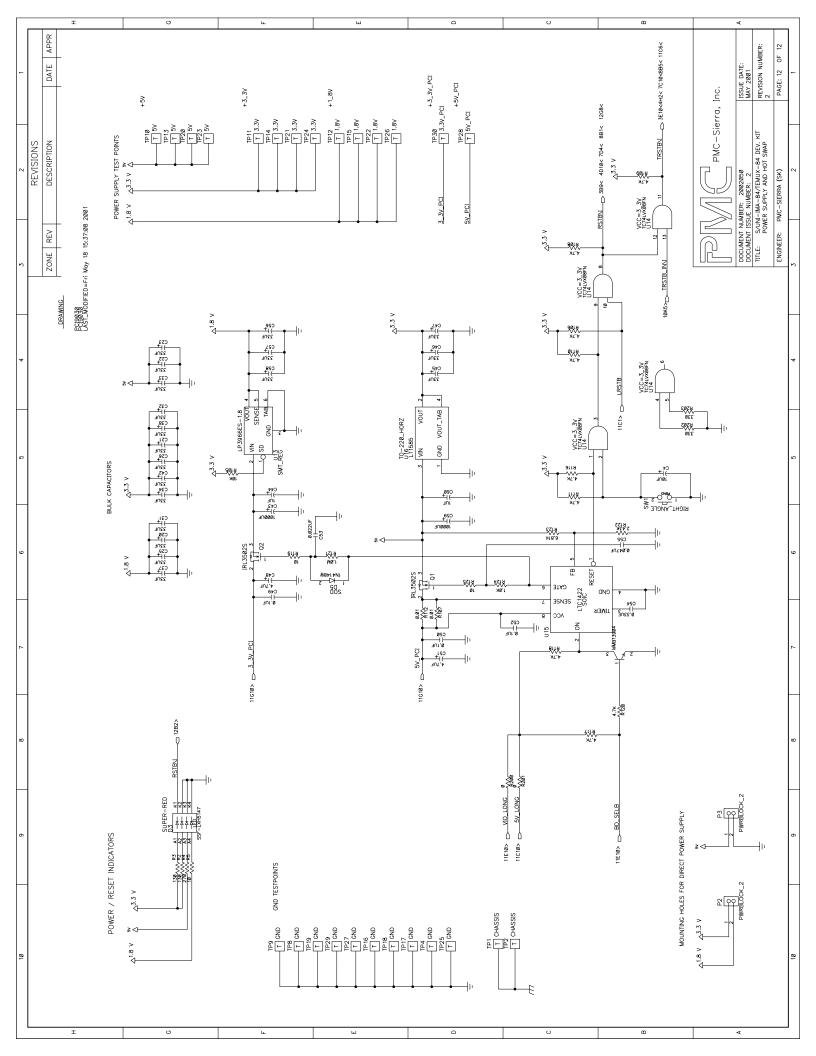

|                                  | 6.1  | POW    | ER SUPPLY             |                                       |

|                                  |      | 6.1.1  | DECOUPLING            |                                       |

|                                  |      | 6.1.2  | POWER-UP SEQUENC      | CE 62                                 |

|                                  | 6.2  | SPEC   | TRA-155 DESIGN CON    | SIDERATIONS 63                        |

|                                  | 6.3  | TEMU   | JX-84 DESIGN CONSIDI  | ERATIONS63                            |

|                                  | 6.4  | S/UN   | -DUPLEX DESIGN CON    | ISIDERATIONS                          |

|                                  | 6.5  | TELE   | COM, SBI, UTOPIA L2 B | BUS DESIGN CONSIDERATIONS 63          |

|                                  | 6.6  | PCI B  | RIDGE DESIGN CONSI    | DERATIONS64                           |

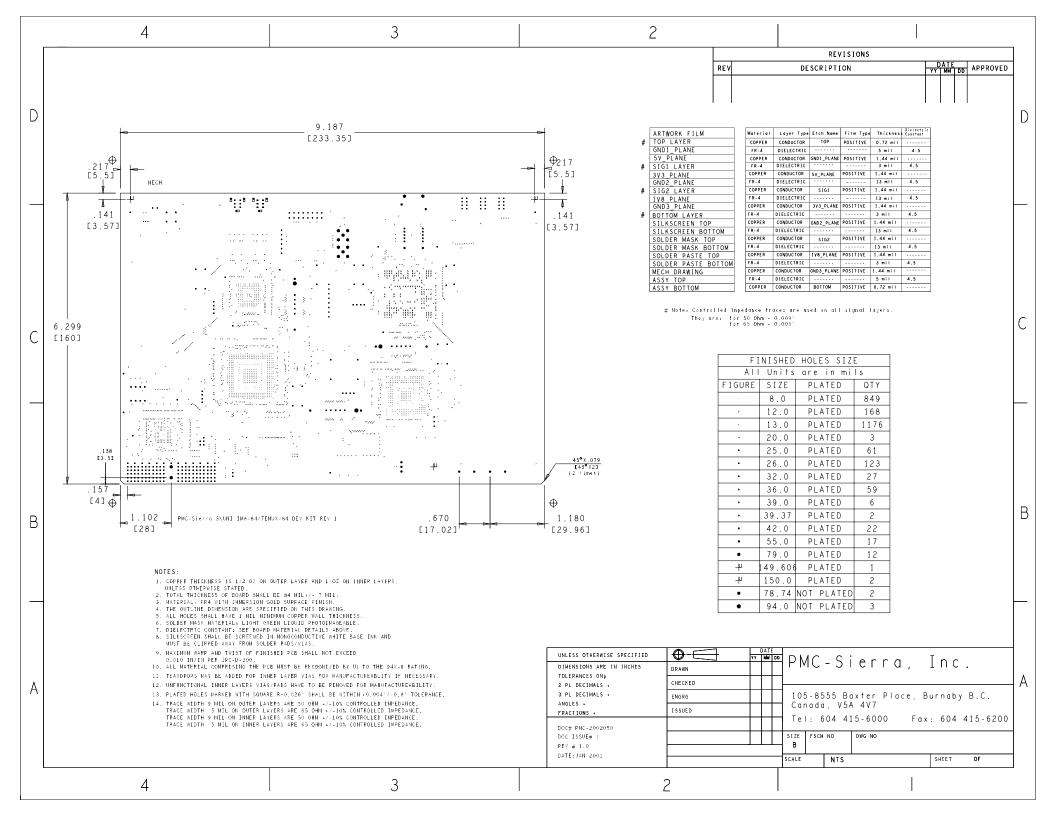

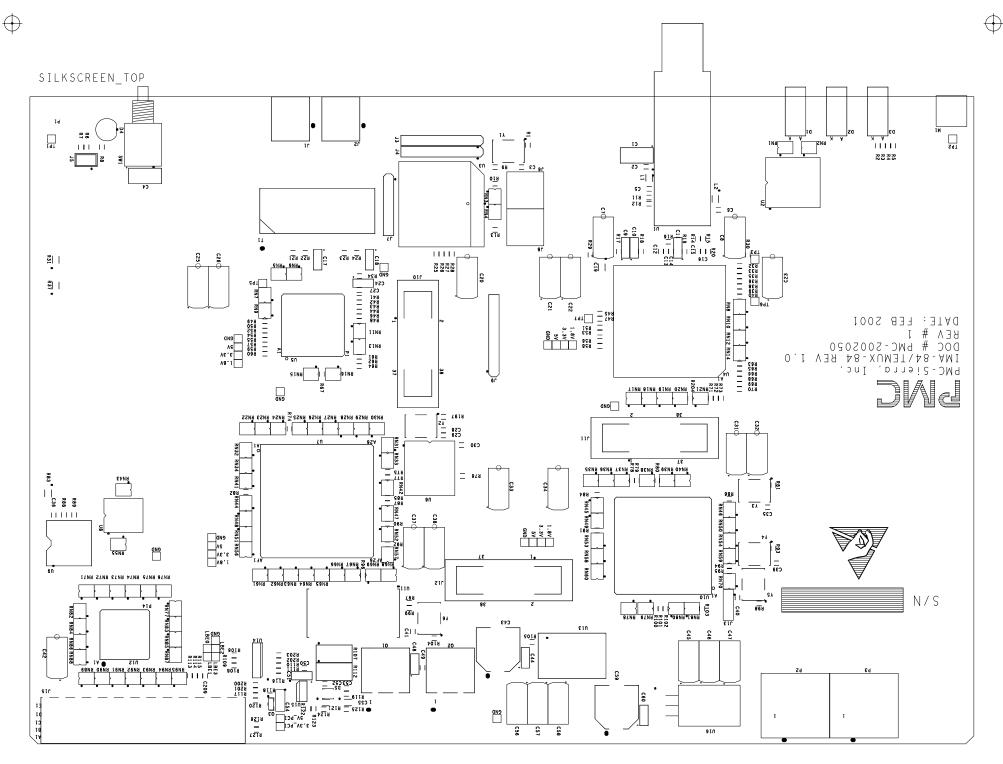

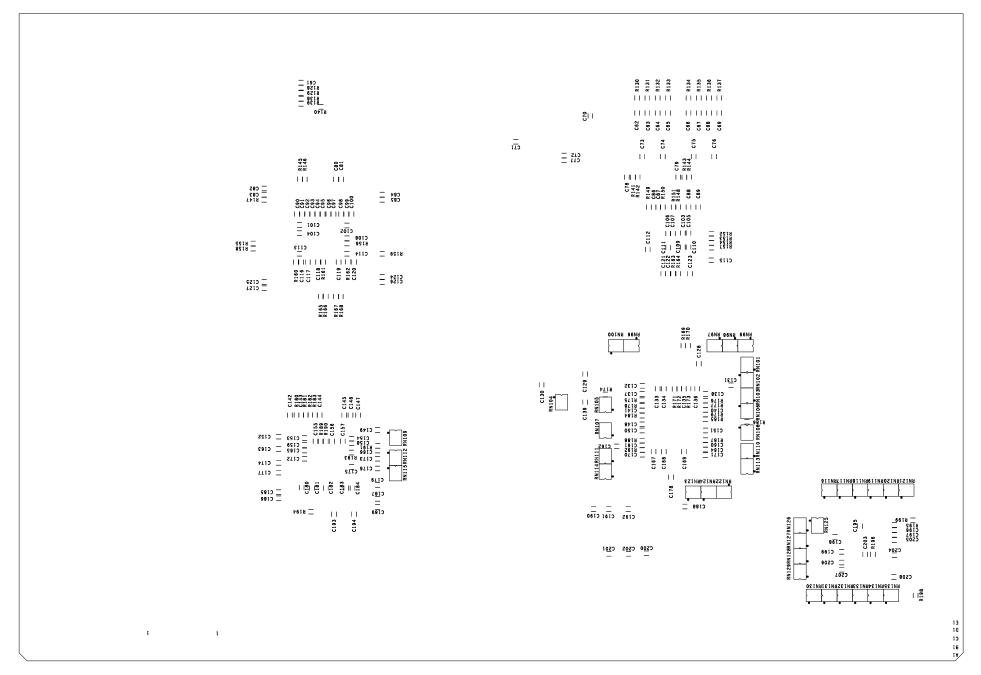

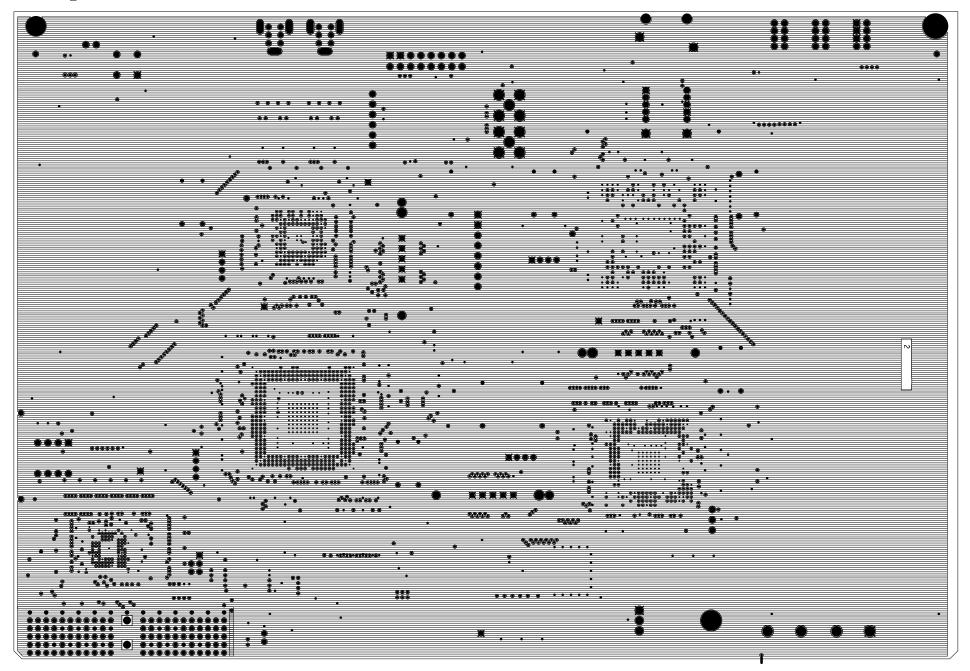

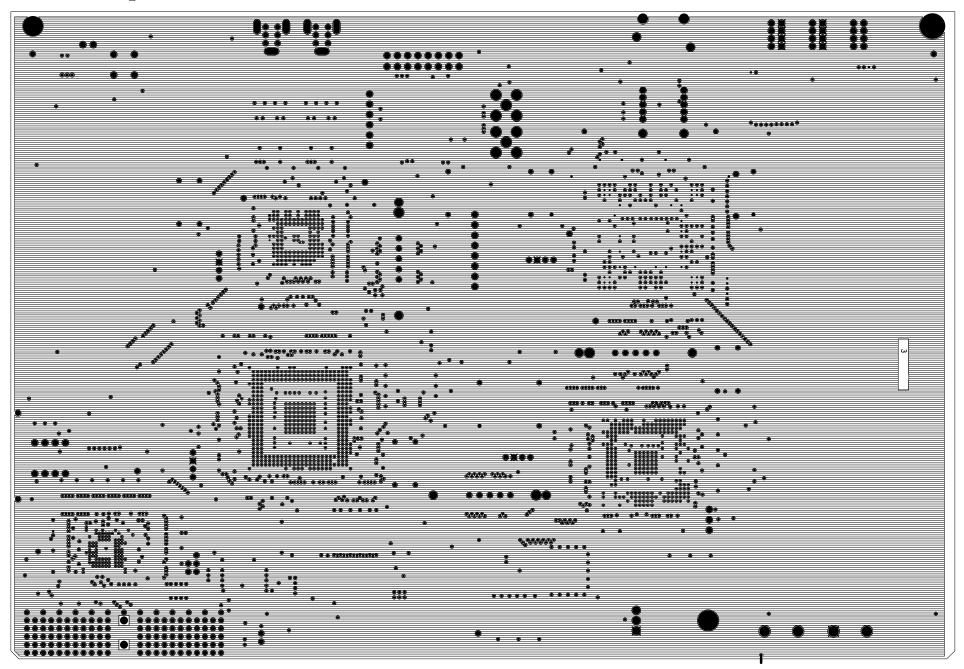

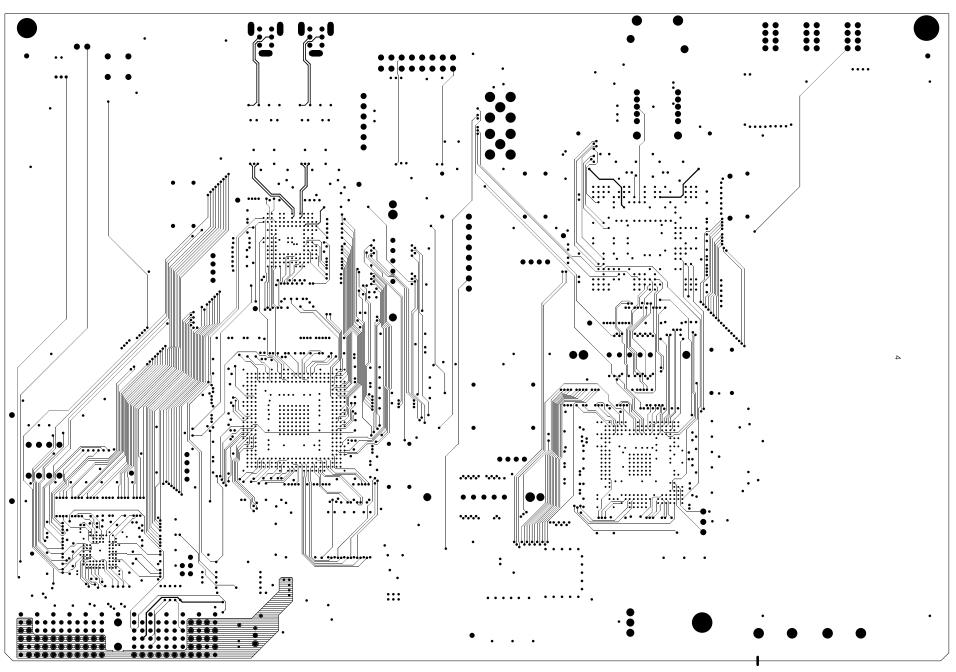

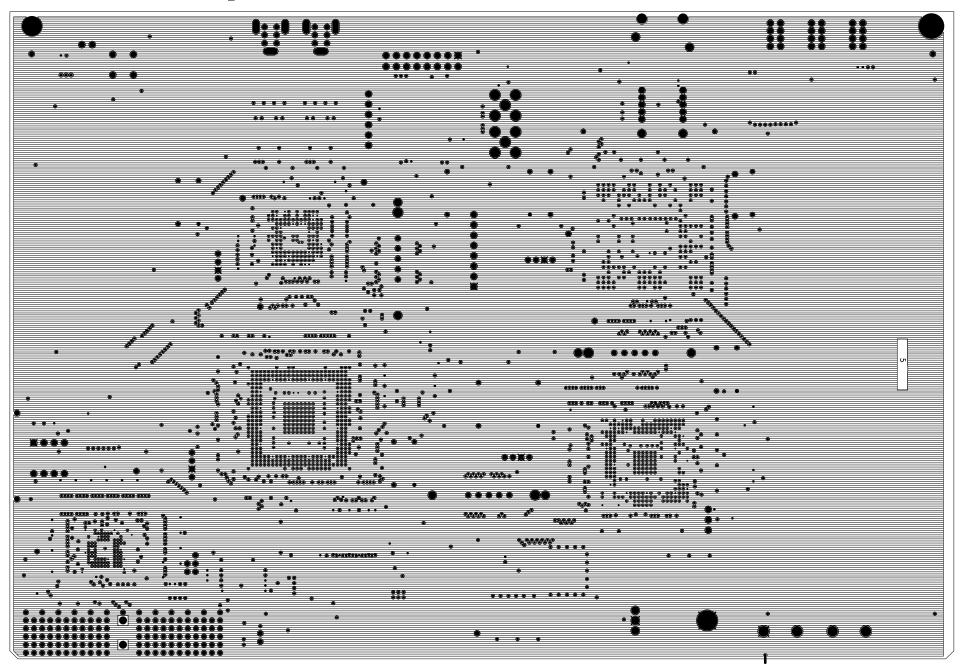

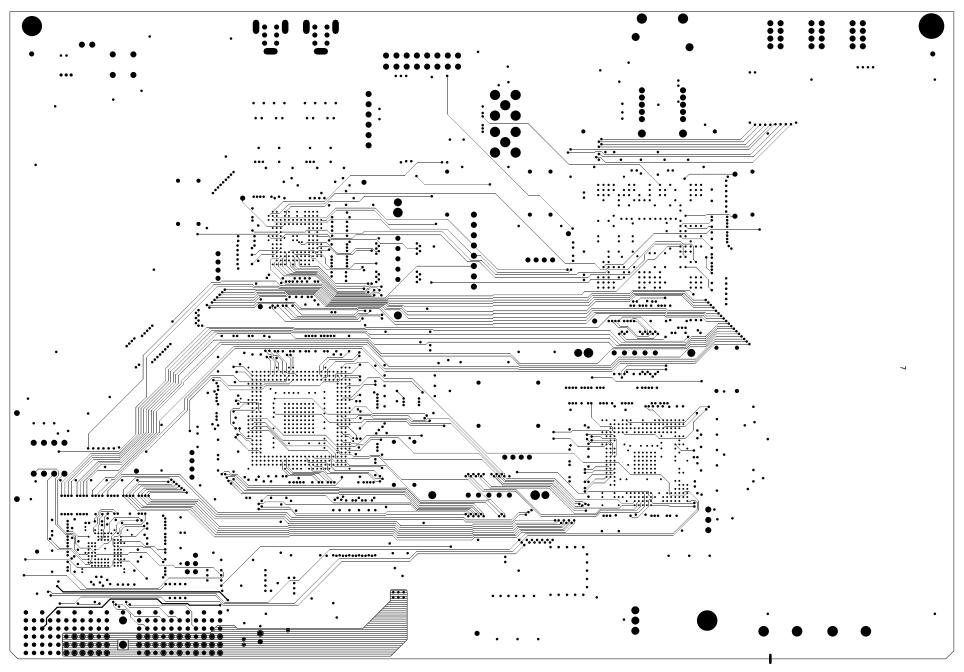

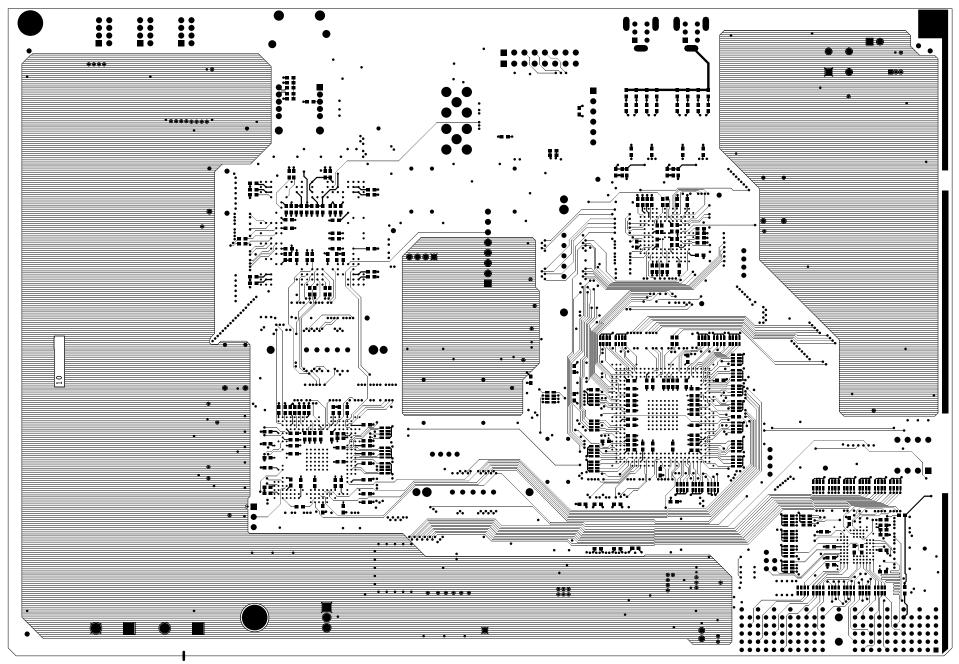

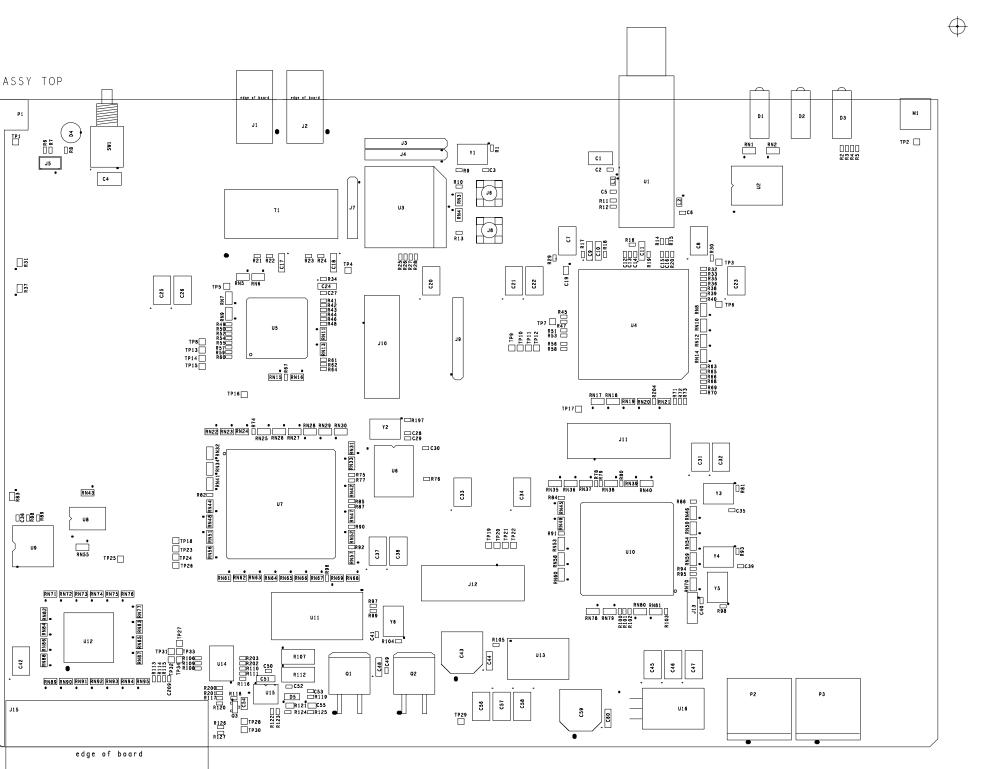

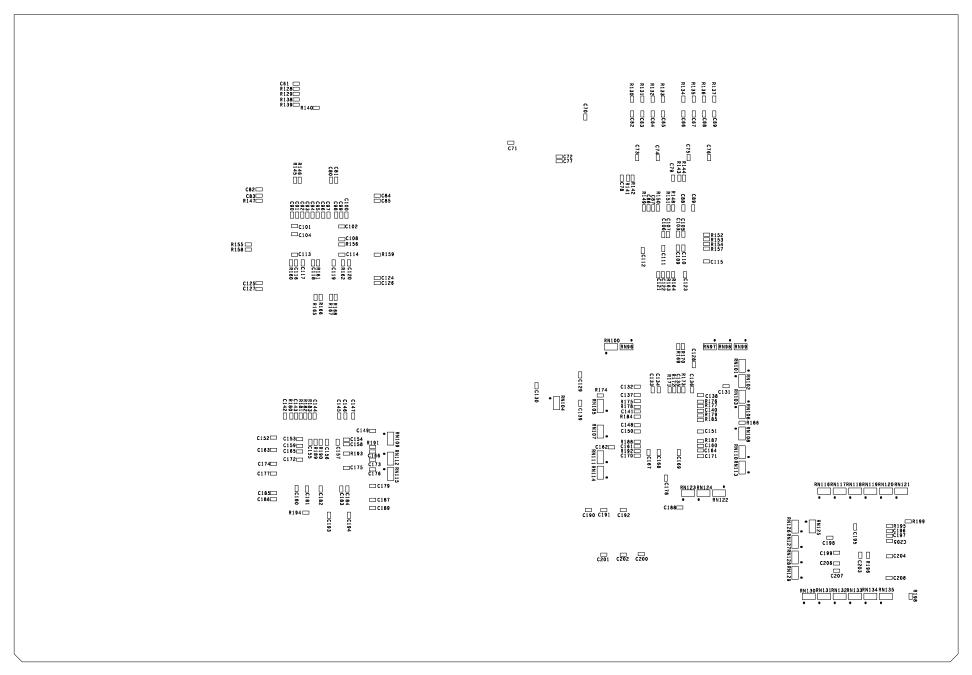

| 7                                | LAYC | OUT DE | SCRIPTION             |                                       |

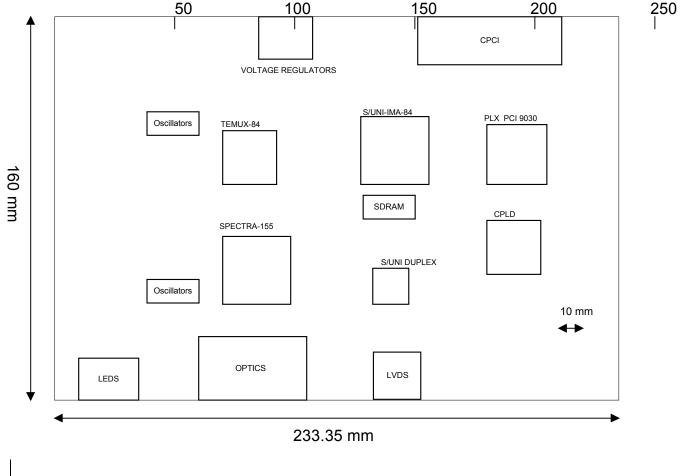

|                                  | 7.1  | COM    | PONENT PLACEMENT .    |                                       |

|                                  | 7.2  | LAYE   | R STACKING AND IMPE   | DANCE CONTROL 67                      |

|                                  | 7.3  | PCI B  | US SIGNAL SPECIFICA   | TION 67                               |

|                                  | 7.4  | ROUT   | TING                  |                                       |

| 8                                | PHYS | SICALA | ND MECHANICAL DES     | CRIPTIONS 68                          |

|                                  | 8.1  | FORM   | I FACTOR              |                                       |

|                                  | 8.2  | LEDS   |                       |                                       |

|                                  |      | 8.2.1  | CARD STATUS LEDS .    |                                       |

|                                  |            |                                        | PM8316 TEMUX-84                       |

|----------------------------------|------------|----------------------------------------|---------------------------------------|

| REFERENCE DESIG<br>PMC - 2002050 | <i>ā</i> N | ISSUE 2                                | S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT |

|                                  |            | 8.2.2 SPECTRA-155 LED'S                |                                       |

| 9                                | SOFT       | WARE INTERFACE                         |                                       |

|                                  | 9.1        | SYSTEM PROCESSOR REQUIRE               | MENT 70                               |

|                                  | 9.2        | S/UNI-IMA-84/TEMUX-84 DEVELO<br>SYSTEM |                                       |

|                                  | 9.3        | DEVICE DRIVERS                         |                                       |

|                                  | 9.4        | S/UNI-IMA-84/TEMUX-84 DEVELO           | PMENT KIT MEMORY MAP 70               |

| 10                               | BOAF       | RD MODIFICATIONS                       |                                       |

|                                  | 10.1       | SIGNAL DETECT ON HFCT 5905             |                                       |

|                                  | 10.2       | UTOPIA L2 BUS                          |                                       |

|                                  | 10.3       | SCANENB PIN ON S/UNI-IMA-84            |                                       |

| 11                               | GLOS       | SSARY                                  |                                       |

| 12                               | REFE       | RENCES                                 |                                       |

| 13                               | APPE       | NDIX A: BILL OF MATERIALS              |                                       |

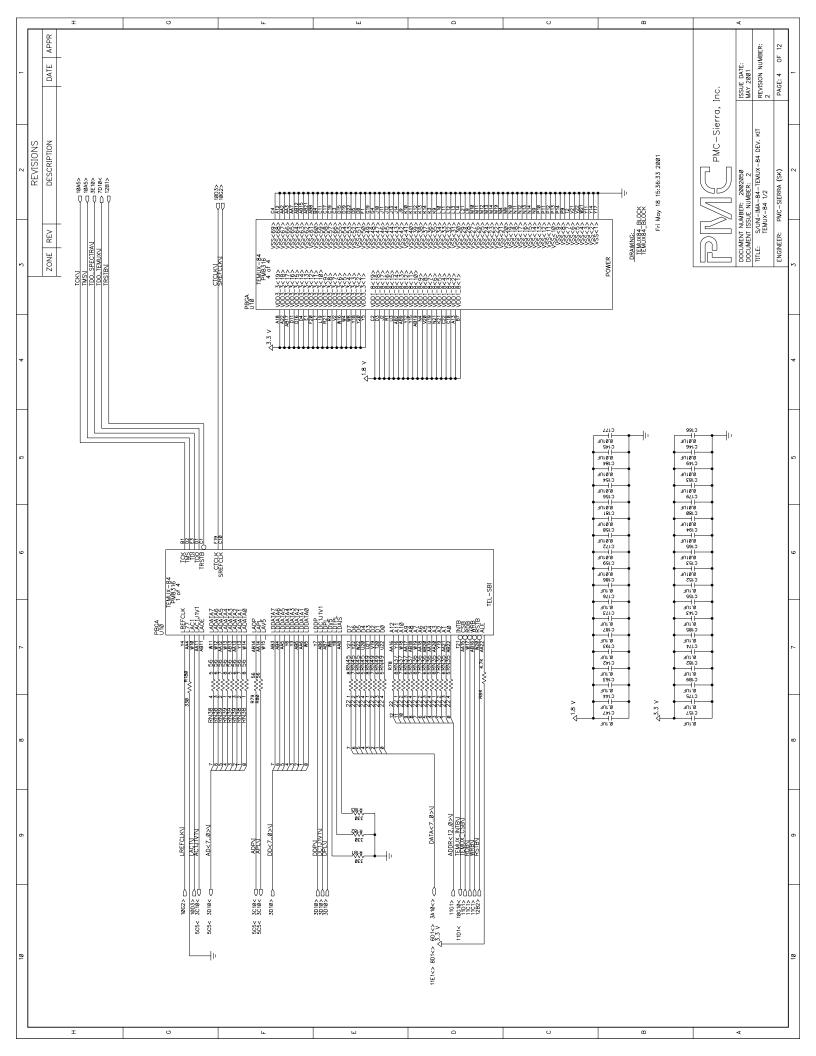

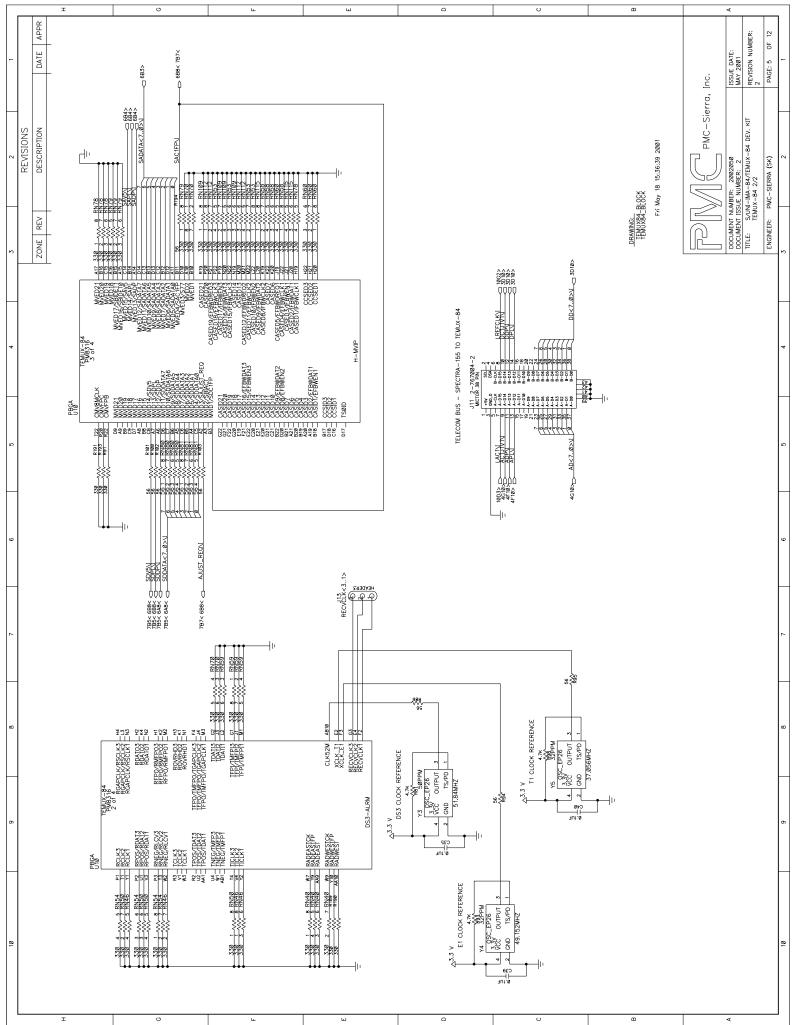

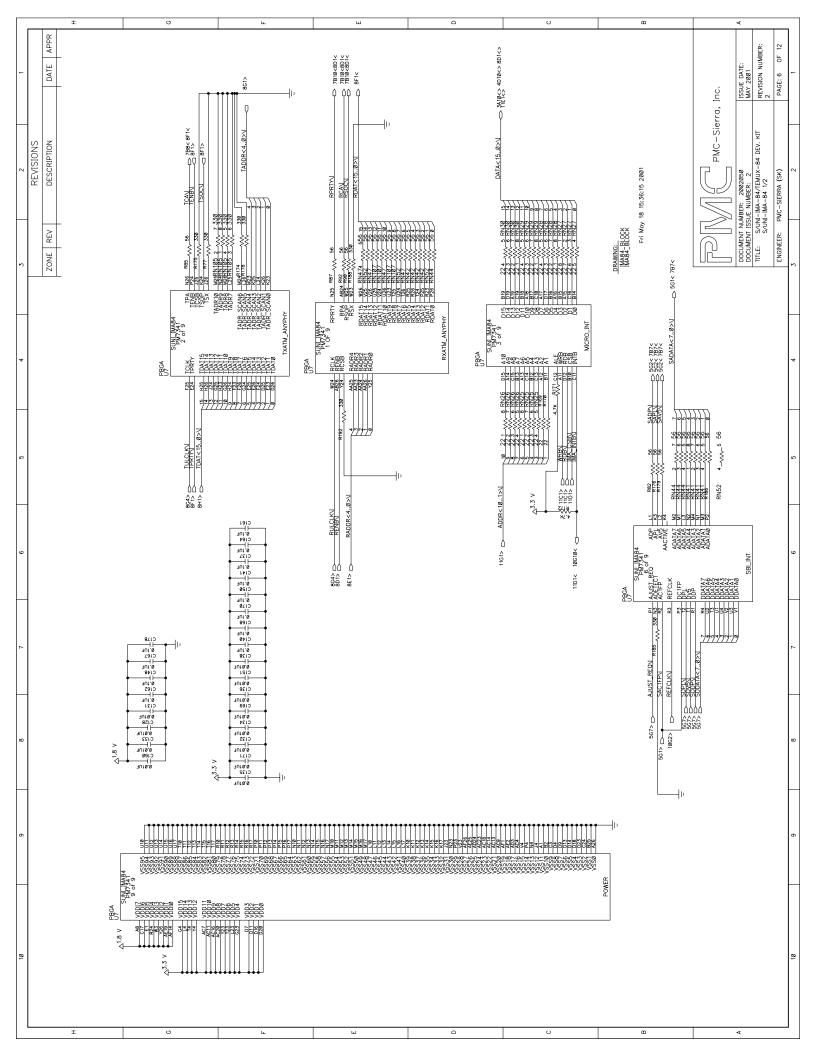

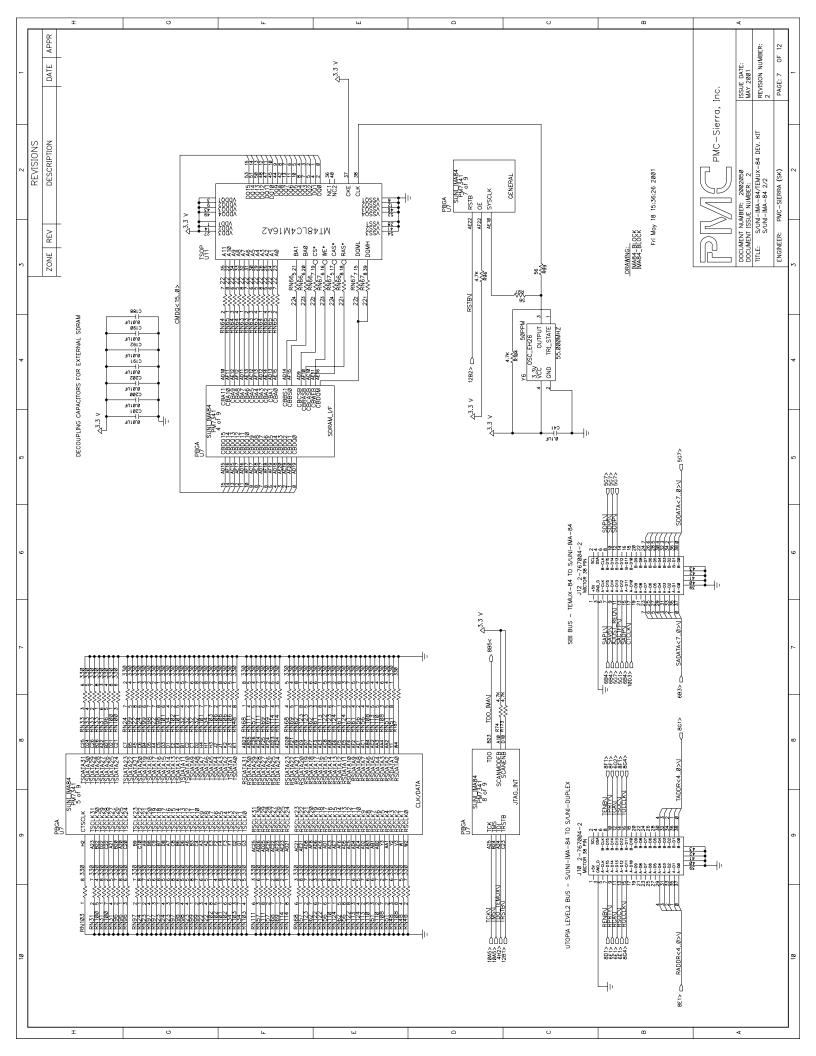

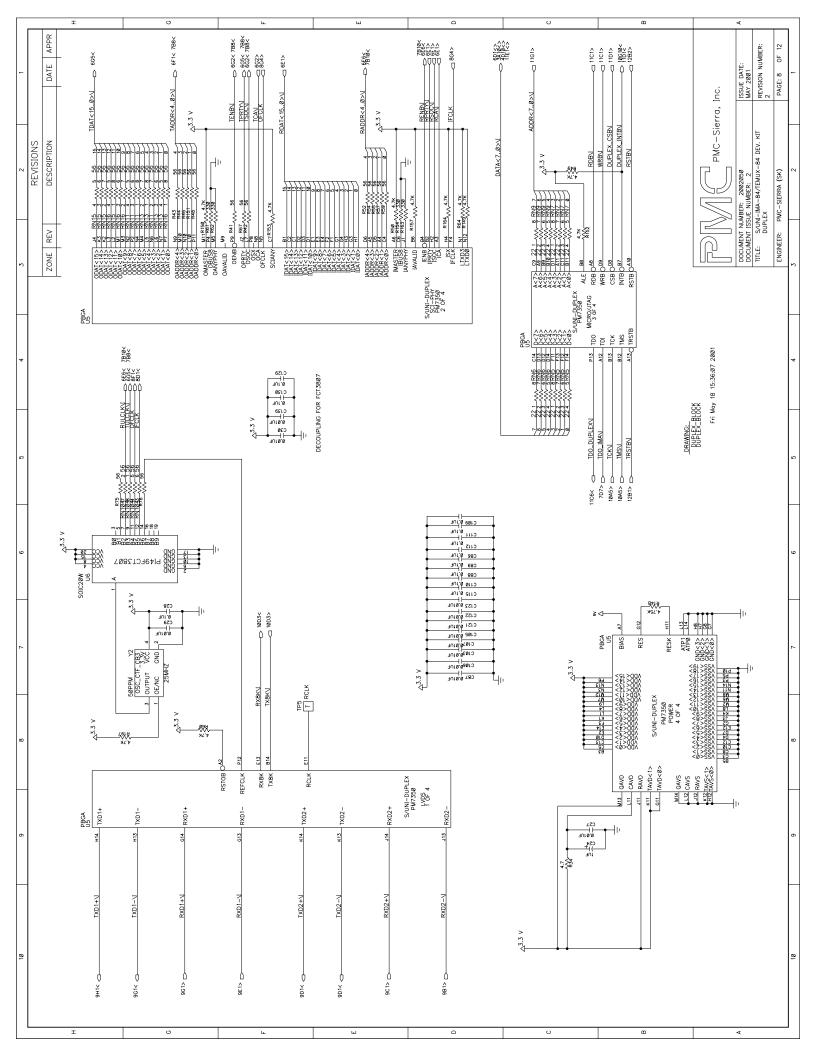

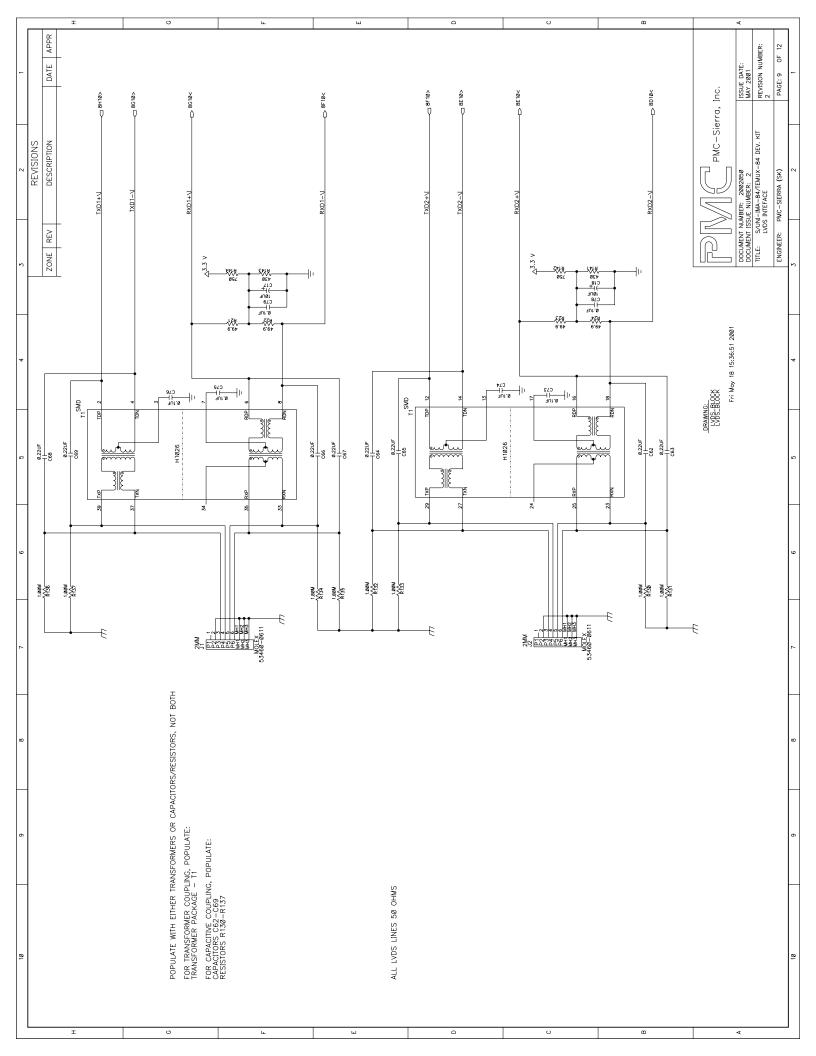

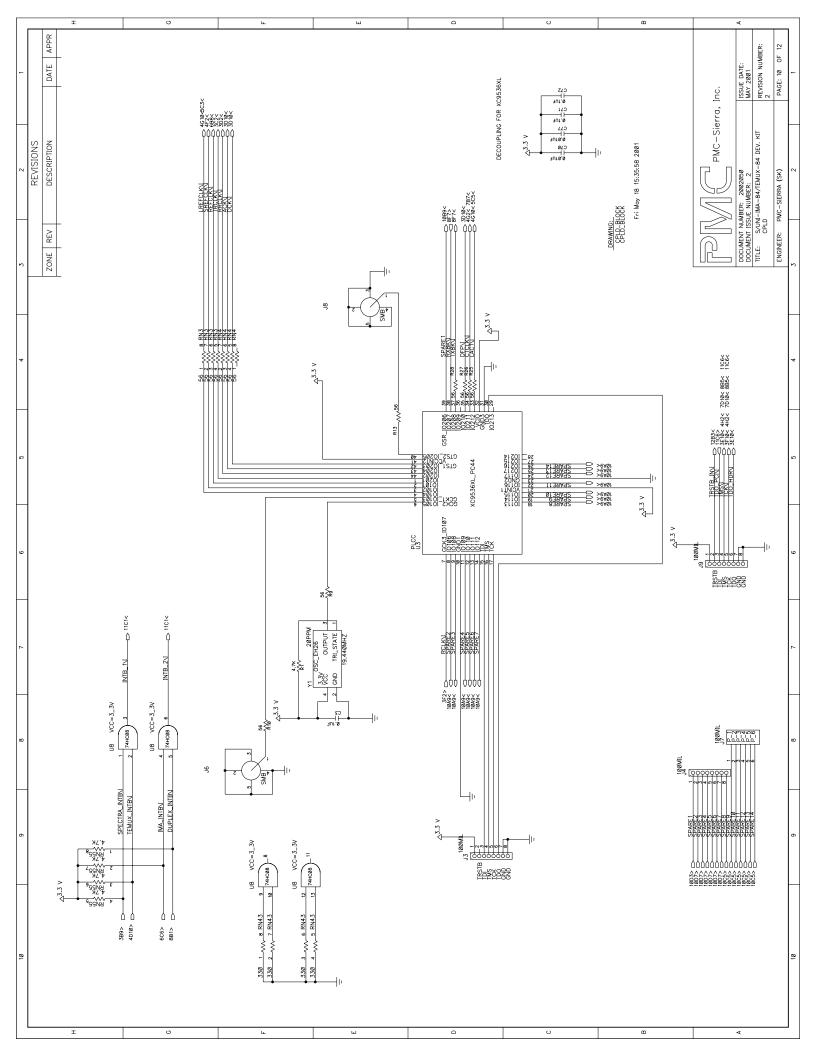

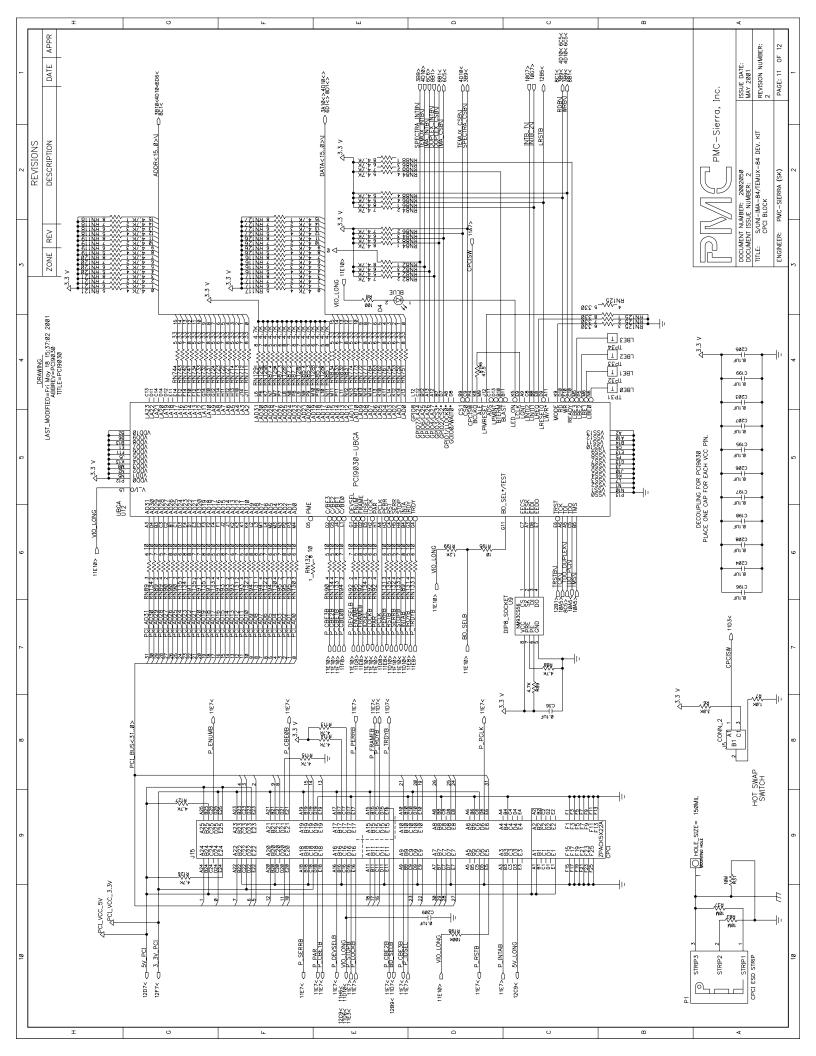

| 14                               | APPE       | NDIX B: SCHEMATICS                     |                                       |

| 15                               | APPE       | NDIX C: LAYOUT                         |                                       |

| 16                               | APPE       | NDIX D: VHDL CODE FOR CPLD             |                                       |

REFERENCE DESIGN PMC - 2002050

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## LIST OF FIGURES

| FIGURE 1 ATM EDGE SWITCH IMA AND UNI PORT CARD EXAMPLE              |

|---------------------------------------------------------------------|

| FIGURE 2 ATM MULTISERVICE SWITCH, ANY SERVICE ANY PORT CARD EXAMPLE |

| FIGURE 3 S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT DATA FLOW 4          |

| FIGURE 4 S/UNI-DUPLEX DEMULTIPLEXING ATM STREAMS 5                  |

| FIGURE 5 IMA PROTOCOL 6                                             |

| FIGURE 6 SONET OC-3 FRAME PROCESSING BY THE SPECTRA-155 8           |

| FIGURE 7 VT1.5 DEMAPPING BY THE TEMUX-84 10                         |

| FIGURE 8 BLOCK DIAGRAM OF S/UNI-IMA-84/ TEMUX-84 DEVELOPMENT<br>KIT |

| FIGURE 9 TELECOM BUS INTERFACE 15                                   |

| FIGURE 10 SBI BUS INTERFACE 16                                      |

| FIGURE 11 UTOPIA LEVEL 2 BUS INTERFACE 17                           |

| FIGURE 12 CPLD LOGIC BLOCK DIAGRAM 23                               |

| FIGURE 14 POWER SUPPLY WITH INTEGRATED HOT SWAP CIRCUITRY 24        |

| FIGURE 15 CPCI SYSTEM BUS INTERFACE BLOCK DIAGRAM                   |

| FIGURE 16 PCI 9030 LOCAL BUS INTERFACE BLOCK DIAGRAM 27             |

| FIGURE 17 TELECOM DROP BUS TIMING DIAGRAM 29                        |

| FIGURE 18 TELECOM ADD BUS TIMING DIAGRAM                            |

| FIGURE 19 SBI ADD BUS TIMING ANALYSIS                               |

| FIGURE 20 SBI DROP BUS TIMING ANALYSIS                              |

| FIGURE 21 UTOPIA L2 BUS TRANSMIT TIMING DIAGRAM                     |

| FIGURE 22 UTOPIA L2 BUS RECEIVE TIMING DIAGRAM                      |

REFERENCE DESIGN PMC - 2002050

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

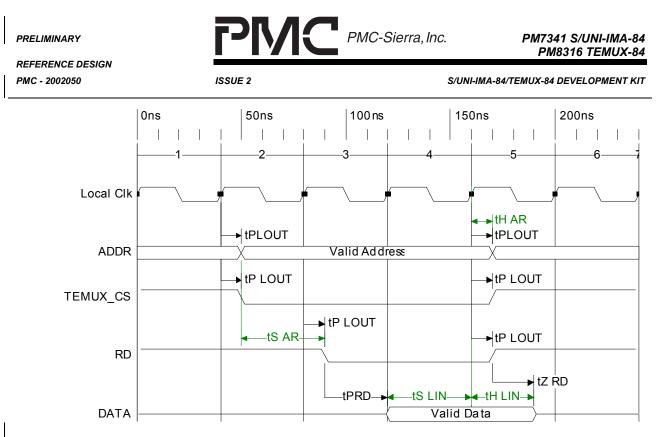

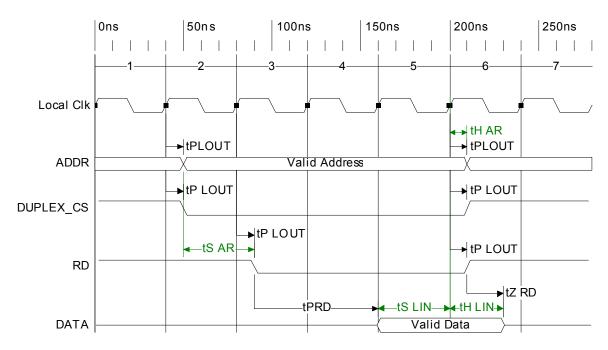

| FIGURE 23 TEMUX-84 READ CYCLE TIMING                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

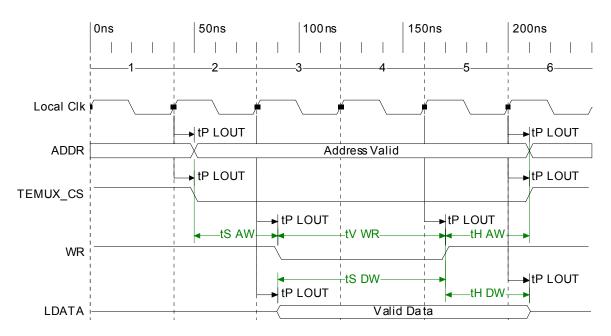

| FIGURE 24 TEMUX-84 WRITE CYCLE TIMING 43                                                                                                                                                                                                     |

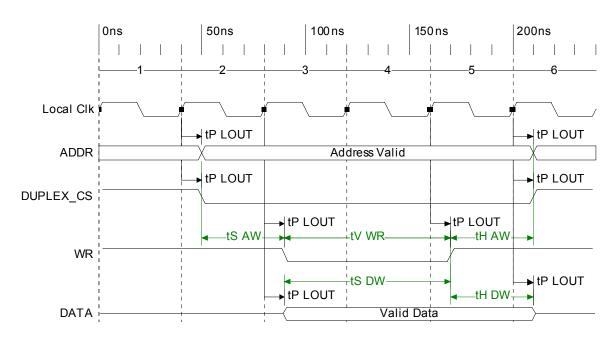

| FIGURE 25 S/UNI-DUPLEX READ TIMING DIAGRAM                                                                                                                                                                                                   |

| FIGURE 26 S/UNI-DUPLEX WRITE TIMING DIAGRAM                                                                                                                                                                                                  |

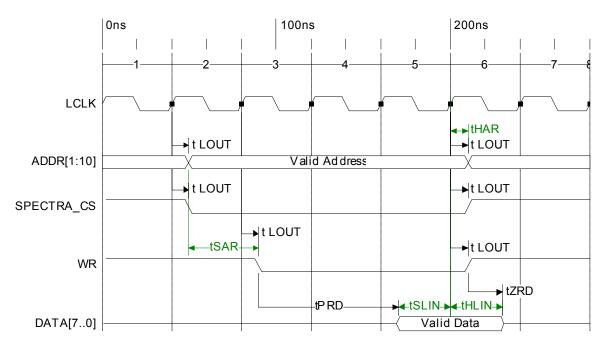

| FIGURE 27 SPECTRA-155 READ CYCLE TIMING 49                                                                                                                                                                                                   |

| FIGURE 28 SPECTRA-155 WRITE CYCLE TIMING 51                                                                                                                                                                                                  |

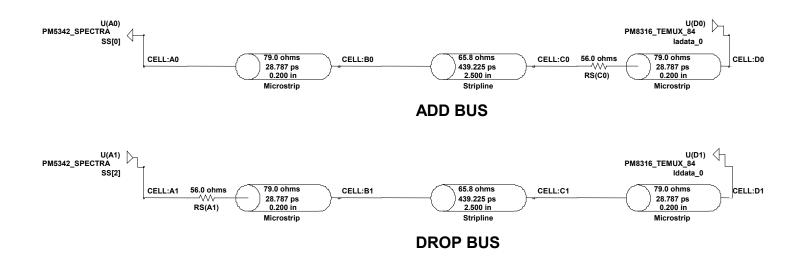

| FIGURE 29 TELECOM BUS SIMULATION SCHEMATIC 53                                                                                                                                                                                                |

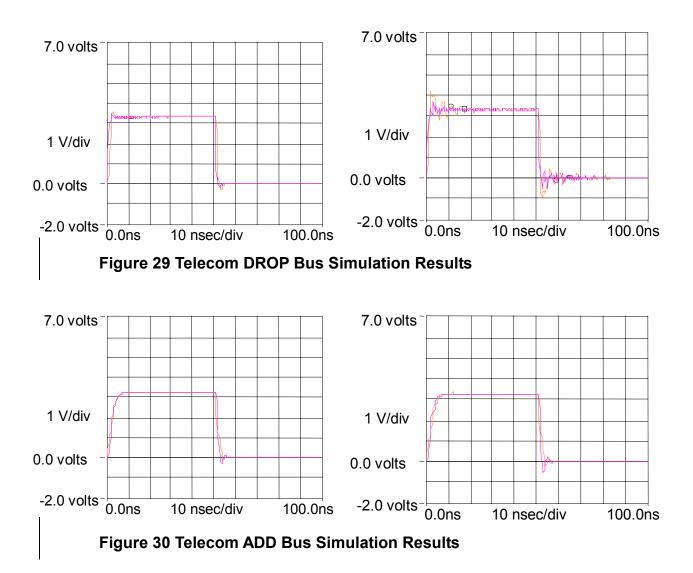

| FIGURE 30 TELECOM DROP BUS SIMULATION RESULTS 54                                                                                                                                                                                             |

| FIGURE 31 TELECOM ADD BUS SIMULATION RESULTS                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                              |

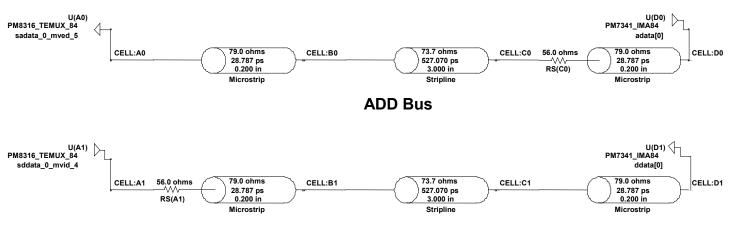

| FIGURE 32 SBI BUS SIMULATION SCHEMATIC 55                                                                                                                                                                                                    |

| FIGURE 32 SBI BUS SIMULATION SCHEMATIC                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                              |

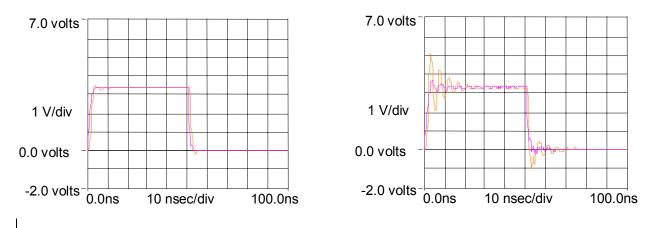

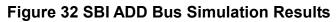

| FIGURE 33 SBI ADD BUS SIMULATION RESULTS                                                                                                                                                                                                     |

| FIGURE 33 SBI ADD BUS SIMULATION RESULTS                                                                                                                                                                                                     |

| FIGURE 33 SBI ADD BUS SIMULATION RESULTS                                                                                                                                                                                                     |

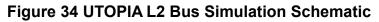

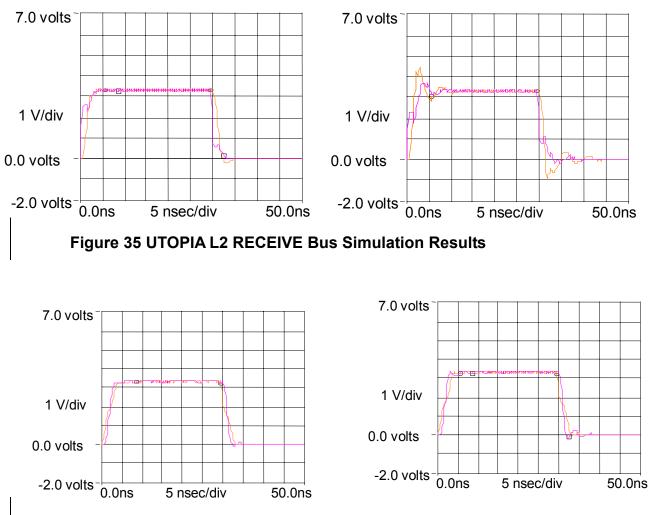

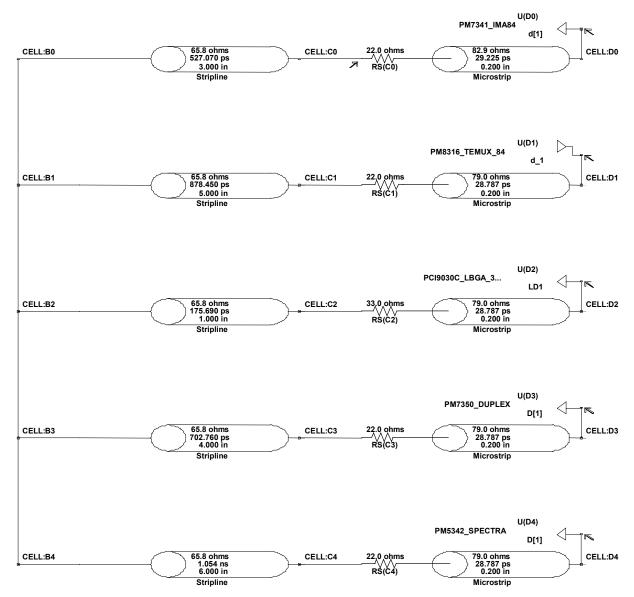

| FIGURE 33 SBI ADD BUS SIMULATION RESULTS55FIGURE 34 SBI DROP BUS SIMULATION RESULTS56FIGURE 35 UTOPIA L2 BUS SIMULATION SCHEMATIC56FIGURE 36 UTOPIA L2 RECEIVE BUS SIMULATION RESULTS57                                                      |

| FIGURE 33 SBI ADD BUS SIMULATION RESULTS55FIGURE 34 SBI DROP BUS SIMULATION RESULTS56FIGURE 35 UTOPIA L2 BUS SIMULATION SCHEMATIC56FIGURE 36 UTOPIA L2 RECEIVE BUS SIMULATION RESULTS57FIGURE 37 UTOPIA L2 TRANSMIT BUS SIMULATION RESULTS57 |

REFERENCE DESIGN PMC - 2002050

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

# LIST OF TABLES

| TABLE 1 PCI CARD ID CODES                                              | 18 |

|------------------------------------------------------------------------|----|

| TABLE 2 PCI 9030 SERIAL EPROM LOAD REGISTERS                           | 19 |

| TABLE 3 TELECOM DROP BUS PROPAGATION DELAYS                            | 30 |

| TABLE 4 TELECOM DROP BUS TIMING CONSTRAINTS                            | 30 |

| TABLE 5 TELECOM ADD BUS PROPAGATION DELAYS                             | 31 |

| TABLE 6 TELECOM ADD BUS TIMING CONSTRAINTS                             | 31 |

| TABLE 7 SBI ADD BUS PROPAGATION DELAYS                                 | 33 |

| TABLE 8 SBI ADD BUS TIMING CONSTRAINTS                                 | 33 |

| TABLE 9 SBI DROP BUS PROPAGATION DELAYS                                | 34 |

| TABLE 10 SBI DROP BUS TIMING CONSTRAINTS                               | 36 |

| TABLE 11 UTOPIA L2 TRANSMIT BUS PROPAGATION DELAYS                     | 38 |

| TABLE 12 UTOPIA L2 TRANSMIT BUS TIMING CONSTRAINTS                     | 38 |

| TABLE 13 UTOPIA L2 RECEIVE BUS PROPAGATION DELAYS                      | 40 |

| TABLE 14 UTOPIA L2 TRANSMIT BUS TIMING CONSTRAINTS                     | 40 |

| TABLE 15 PCI 9030 AC TIMING (LOCAL INPUTS) ELECTRICAL CHARACTERISTICS  | 41 |

| TABLE 16 PCI 9030 AC TIMING (LOCAL OUTPUTS) ELECTRICAL CHARACTERISTICS | 41 |

| TABLE 17 PCI 9030 TO TEMUX-84 READ PROPAGATION DELAYS                  | 43 |

| TABLE 18 PCI 9030 TO TEMUX-84 READ TIMING CONSTRAINTS                  | 43 |

| TABLE 19 PCI 9030 TO TEMUX-84 WRITE PROPAGATION DELAYS                 | 44 |

| TABLE 20 PCI 9030 TO TEMUX-84 WRITE TIMING CONSTRAINTS                 | 44 |

| TABLE 21 PCI 9030 TO S/UNI-DUPLEX READ PROPAGATION DELAYS              | 46 |

REFERENCE DESIGN PMC - 2002050

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

TABLE 22 PCI 9030 TO S/UNI-DUPLEX READ TIMING CONSTRAINTS...... 46 TABLE 23 PCI 9030 TO S/UNI-DUPLEX WRITE PROPAGATION DELAYS ... 48 TABLE 24 PCI 9030 TO S/UNI-DUPLEX WRITE TIMING CONSTRAINTS ..... 48 TABLE 25 PCI 9030 TO SPECTRA-155 READ PROPAGATION DELAYS ...... 50 TABLE 26 PCI 9030 TO SPECTRA-155 READ TIMING CONSTRAINTS...... 50 TABLE 27 PCI 9030 TO SPECTRA-622 WRITE PROPAGATION DELAYS ...... 52 TABLE 28 PCI 9030 TO SPECTRA-622 WRITE TIMING CONSTRAINTS ..... 52 TABLE 29 POWER CONSUMPTION BY SUPPLY RAIL FOR EACH DEVICE 60 TABLE 30 S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT MEMORY MAP ... 70

PMC PMC-Sierra, Inc.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## 1 INTRODUCTION

The S/UNI-IMA-84/TEMUX-84 Development Kit is intended for software development of several PMC-Sierra devices including:

- SPECTRA-155

- TEMUX-84

- S/UNI-IMA-84

- S/UNI-DUPLEX

#### 1.1 Purpose

The S/UNI-IMA-84/TEMUX-84 Development Kit is intended to assist engineers in board design and software development using PMC-Sierra's PM7341 S/UNI-IMA-84, PM8316 TEMUX-84, PM5342 SPECTRA-155 and PM7350 S/UNI-DUPLEX.

The S/UNI-IMA-84/TEMUX-84 Development Kit can also be used to generate a high speed Low Voltage Differential Signal (LVDS) serial link for connection to other PMC-Sierra devices with an LVDS interface.

#### 1.2 Scope

This document describes the design of the S/UNI-IMA-84/TEMUX-84 Development Kit. A description for each of the functional blocks of the design is given followed by the detailed design, including physical and mechanical descriptions, implementation descriptions, layout, bill of materials and CPLD code.

#### 1.3 Applications

## 1.3.1 ATM Edge Switch IMA and UNI Port Card

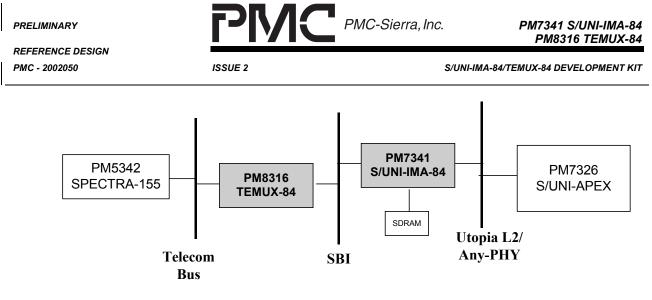

An optimized solution comprising the PM7341 S/UNI-IMA-84 and PM8316 TEMUX-84 devices enables a new generation of high-density port cards for terminating up to an OC-3s worth of IMA circuits (84 T1 links). The following Figure shows the S/UNI-IMA-84 connected to a TEMUX-84, SDRAM and an ATM Layer Device.

## 1.1.1 ATM Multiservice Switch, Any Service Any Port Card

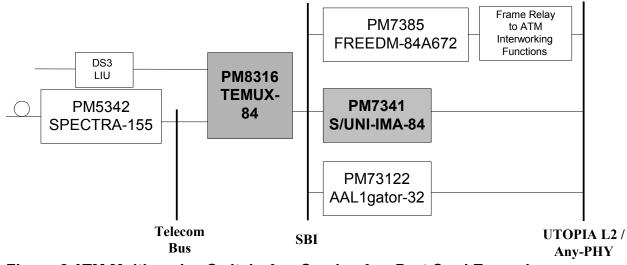

The following Figure shows an ATM Multiservice Switch Any Service, Any Port card comprising the PM7341 S/UNI-IMA-84, PM7385 FREEDM-84A672, Frame Relay to ATM Interworking Functions, PM73122 AAL1gator-32, PM8316 TEMUX-84, PM5342 SPECTRA-155 and a DS3 LIU. Through software configuration of the devices, any port can be configured to support IMA, User-to-Network Interfaces (UNI), Frame Relay or Circuit Emulation Service.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

#### 2 FEATURES

This Reference Design provides the following features:

- Provides full access to the SPECTRA-155, TEMUX-84, S/UNI-IMA-84, S/UNI-DUPLEX registers.

- 33 MHz CompactPCI (CPCI) interface.

- On board hot swap controller with power sequencing.

- 3.3 Volt CMOS Telecom bus allowing communication between the SPECTRA-155 and the TEMUX-84.

- 19.44 MHz SBI bus allowing communication between the TEMUX-84 and the S/UNI-IMA-84.

- UTOPIA Level 2 bus allowing communication between the S/UNI-IMA-84 and the S/UNI-DUPLEX.

- Two LVDS serial links provided for applications that need 1:1 protection such as connection to the DSLAM Core Card (part of the DSLAM Reference Design) for connection to WAN up-link.

- Front panel status LED's which display line status and power supply status.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## 3 FUNCTIONAL DESCRIPTION

#### 3.1 Data Flow

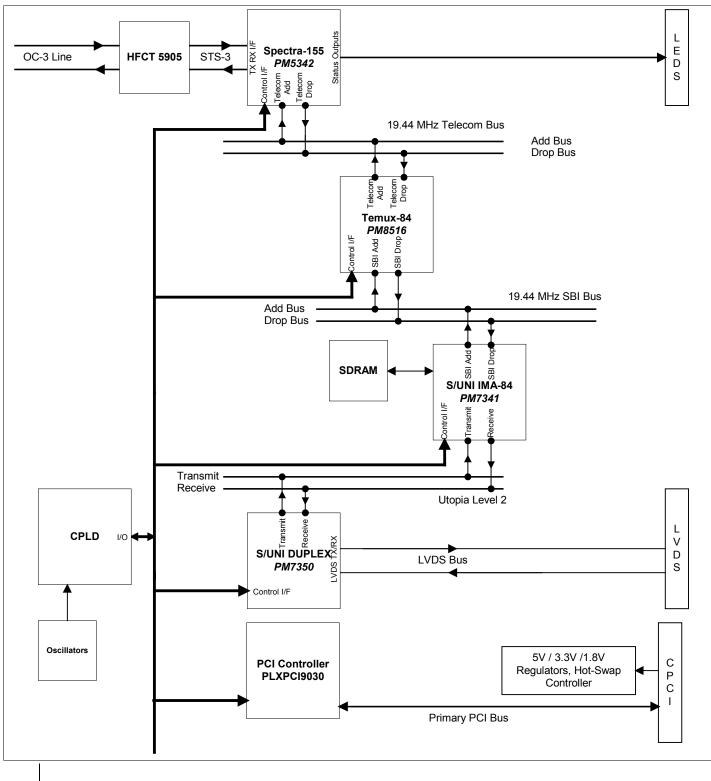

The S/UNI-IMA-84/TEMUX-84 Development Kit is connected over a CompactPCI bus to a host processor and external memory. Figure 3 illustrates the general data flow.

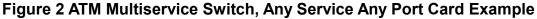

#### Figure 3 S/UNI-IMA-84/TEMUX-84 Development Kit Data Flow

#### 3.1.1 Transmit Direction

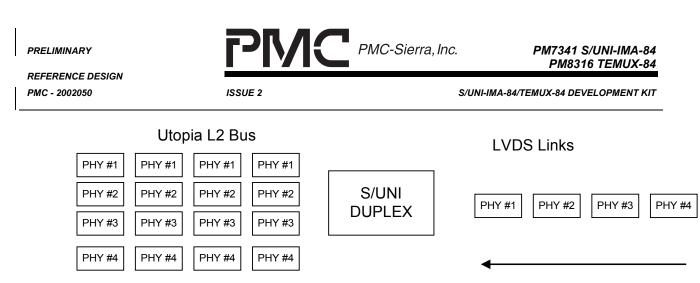

In the transmit direction, the S/UNI-DUPLEX receives data via the LVDS interface. The S/UNI-DUPLEX demultiplexes these ATM cells and routes them to the appropriate virtual PHY of the S/UNI-IMA-84 via the UTOPIA L2 bus.

Four Single ATM Streams

One Multiplexed ATM Stream

## Figure 4 S/UNI-DUPLEX Demultiplexing ATM Streams

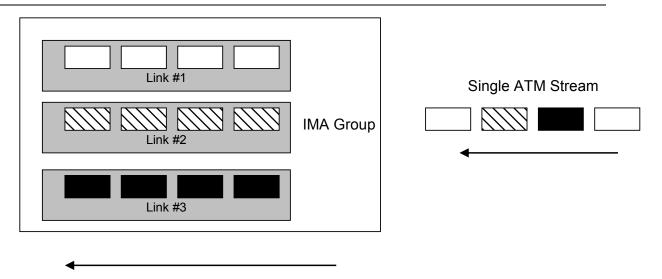

The S/UNI-IMA-84 performs the IMA protocol on the data recovered from the UTOPIA L2 bus. The IMA protocol consists of taking a cell stream destined to a group and distributing the cells in a round-robin fashion to the links within a group, adding IMA Control Protocol (ICP) cells, filler cells and stuff cells as needed. The ICP cells convey state information to the far end and are used to format an IMA frame. The IMA frame is used as a mechanism to synchronize the links at the far end. Cell rate decoupling is performed at the IMA sub-layer via filler cells. Filler cells are used instead of physical layer cells for cell rate decoupling, thus a continuous stream of cells is sent to the TC layer.

By distributing the ATM cell stream to multiple physical links in a round-robin fashion, an IMA Group appears to the ATM layer devices like a PHY layer device with a maximum capacity which is determined by the number of links per group the S/UNI-IMA-84 is configured to support (e.g. nxT1, nxE1, nxG.SHDSL). The S/UNI-IMA-84 supports up to 42 simultaneous IMA groups and each IMA group can support 1 to 32 links with the constraint of a maximum of 84 total links. However, because the S/UNI-IMA-84 is configured in UTOPIA L2 mode (as opposed to Any-PHY) and because UTOPIA L2 only supports 31 PHYs, only up to a maximum of 31 virtual PHYs can be addressed within the S/UNI-IMA-84.

An IMA Group is referred to as a virtual PHY because the ATM layer can address multiple virtual PHYs within one physical PHY device, the S/UNI-IMA-84. In this design, an IMA link refers to the individual T1 line, down which a portion of the Group's ATM traffic travels.

An IMA layer device on the other end of the physical links will reassemble the ATM cells arriving from the various physical links into a single ATM stream, which it will pass to the ATM layer.

PMC - 2002050

REFERENCE DESIGN

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

#### Figure 5 IMA Protocol

In the TC sub-layer, the HEC is calculated and inserted into the cell headers. The cell stream is then mapped into the DS1 payload with zeros inserted for the framing and overhead bits.

After a serial to parallel conversion is performed on the 84 links, the data is then conveyed across the SBI ADD bus to the TEMUX-84.

The EXSBI (Extract Scaleable Bandwidth Interconnect) block of the TEMUX-84 device demaps up to 84 1.544Mb/s links, 63 2.048Mb/s links or three 44.736Mb/s links from the SBI ADD bus. Timing for the links can be slaved to the arrival rate of data or from link rate adjustments provided by the TEMUX-84. In this design, the TEMUX-84 is configured in master mode. The TEMUX-84 can also send link rate adjustment requests to the S/UNI-IMA-84 using the AJUST\_REQ signal. This signal indicates whether the S/UNI-IMA-84 should send one additional or one fewer byte of data during the next 500 µs interval.

Each T1 transmitter frames to SF or ESF DS1 formats, or framing can be optionally disabled. The TEMUX-84 supports signaling insertion, idle code substitution, data insertion, line loopback, data inversion and zero-code suppression on a per-DS0 basis. PRBS generation or detection is supported on a framed and unframed T1 basis.

The SPE's from the TEMUX-84 are transmitted to the SPECTRA-155 devices via the TELECOM ADD Bus.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

Each TPIP (Transmit Pointer Interpreter) block within the SPECTRA-155 takes the SPEs from the TELECOM ADD Bus and interprets the H1, H2 pointers, indicates the J1 byte location, and detects alarm conditions. The TTAL (Transmit Telecombus Aligner) block then takes the STS-1 SPE from the TPIP, and aligns it to the frame of the transmit stream. The TPOP (Transmit Path O/H Processor) block then performs path overhead processing. Following this, both Line and Section Overhead processing occurs before the complete SONET STS-3 SPE is transmitted serially over transmit line interface.

The transmitted signal is then converted to optical format by the front panel Optical Interface unit.

#### 3.1.2 Receive Direction

The S/UNI-IMA-84/TEMUX-84 Development Kit receives SONET/SDH OC-3 (155.52 Mbits\s) frames through the front panel optical interface. The optical interface converts the optical signals into STS-3 (155.52 Mbits\s) electrical signals for processing by the SPECTRA-155.

The SPECTRA-155 receives SONET/SDH frames via a bit serial interface, recovers clock and data, and terminates the SONET/SDH section (regenerator section), line (multiplexer section), and path. It performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section and line bit interleaved parity (BIP) (B1, B2), accumulating error counts at each level for performance monitoring purposes. B2 errors are also monitored to detect signal fail and signal degrade threshold crossing alarms (for use with Automatic Protection Switching). Line remote error indications (M1) are also accumulated.

In addition, the SPECTRA-155 interprets the received payload pointers (H1, H2), detects path alarm conditions, detects and accumulates path BIPs (B3). The SPECTRA-155 also monitors and accumulates path Remote Error Indications (REIs), accumulates and compares the 16 or 64 byte path trace (J1) message against an expected result, and extracts the Synchronous Payload Envelope (virtual container).

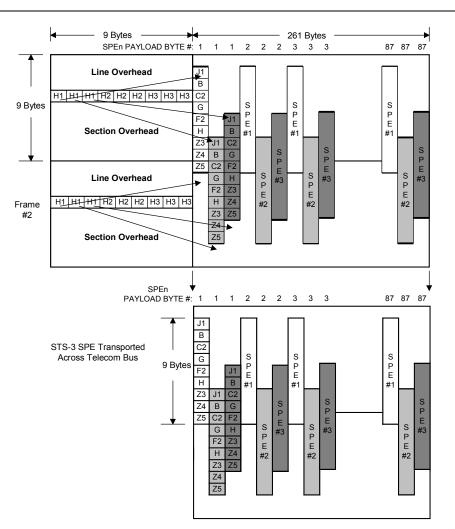

Figure 6 below depicts the format of an incoming SONET STS-3 Frame using floating SPE structures. The SPE's are located using the H1 and H2 pointer bytes.

PMC - 2002050

**REFERENCE DESIGN**

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## Figure 6 SONET OC-3 Frame Processing by the SPECTRA-155

The extracted SPE is placed on the Telecom DROP bus. The DPL (DROP Bus Payload Active) and DC1J1V1 (DROP Bus Composite Timing) signals indicate the location of the path overhead and the tributaries within the SPE.

The TEMUX-84 device receives data placed on the TELECOM DROP Bus. The TEMUX-84 is configured to use a Telecom Bus (SONET\SDH) Line Side Interface and the SBI Bus System Side Interface.

The SONET/SDH line side interface provides STS-1 SPE processing and generation. The payload processor aligns and monitors the performance of SONET virtual tributaries (VT1.5s). Maintenance functions per tributary include loss of pointer detection, AIS alarm, tributary path signal label mismatch, and tributary path signal label unstable alarms. Optionally, interrupts can be generated due to the assertion and removal of any of the above alarms. Counts

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

are accumulated for tributary path BIP-2 errors on a block or bit basis and for FEBE indications. The synchronous payload envelope generator generates all tributary pointers and calculates and inserts tributary path BIP-2. The generator also inserts FEBE, RDI and enhanced RDI in the V5 byte. Software can force AIS insertion on a per tributary basis.

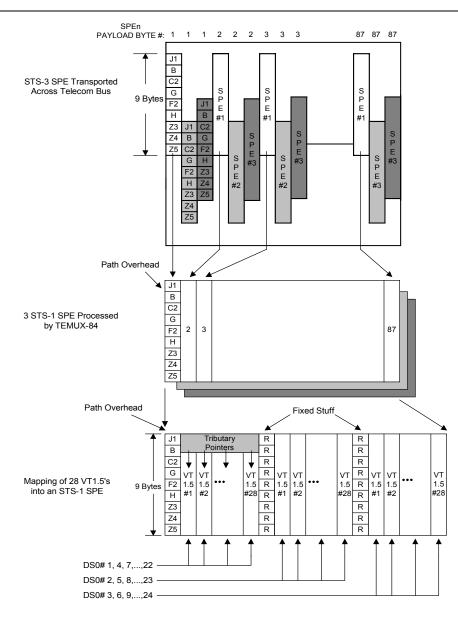

The TEMUX-84 SONET/SDH VT Payload Processor demaps up to 84 T1s from the three STS-1 SPEs (AU3 or TUG3). The bit asynchronous demapper performs majority vote C-bit decoding to detect stuff requests for T1, E1 and DS3 asynchronous mappings. The VT1.5/VT2/TU-11/TU-12 mapper uses an elastic store and a jitter attenuator to minimize jitter introduced via bit stuffing.

Figure 7 depicts how the individual STS-1 SPE's (carried within the STS-3 SPE) transmitted across the Telecom Drop Bus are processed by the TEMUX-84. The TEMUX-84 is configured to process three STS-1 SPEs and it utilizes the tributary pointers to locate the beginning of each VT1.5. Figure 7 also shows how each VT1.5 is mapped into the STS-1 SPE.

REFERENCE DESIGN

PMC - 2002050

PMC-Sierra, Inc.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## Figure 7 VT1.5 Demapping by the TEMUX-84

The S/UNI-IMA-84 implements the Transmission Convergence (TC) layer function and Inverse Multiplexing for ATM (IMA) protocol for DS1/E1 links.

The TC layer searches for cell delineation as per the procedures outlined in ITU-T Recommendation I.432.1. To find the cell delineations, the TC layer computes the HEC value for all bits received. Once cell delineation is obtained, the payload is optionally descrambled and the cells are passed to the IMA sub-layer. The TC layer provides counts of errored headers as well as OCD and LCD error interrupts.

REFERENCE DESIGN PMC - 2002050

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

The IMA sub-layer performs IMA frame delineation and stuff cell removal. IMA delineation consists of reassembling a single ATM stream, running at some multiple of the T1 rate, out of the ATM cells arriving over the multiple physical links. Based upon the ICP cell information, the S/UNI-IMA-84 determines the differential delay between the links within a group and applies the link and group state machine logic to coordinate the activation and deactivation of the groups and links with the far end. The recovered ATM cells are transmitted across a Utopia L2 interface running at 25 MHz to the S/UNI-DUPLEX.

The S/UNI-DUPLEX implements the first stage of multiplexing by routing traffic from the IMA's virtual PHYs and transmitting the traffic simultaneously over two high speed serial 4 wire LVDS providing 1:1 protection for possible interface to a core card for connection to a WAN up-link.

**ISSUE 2**

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

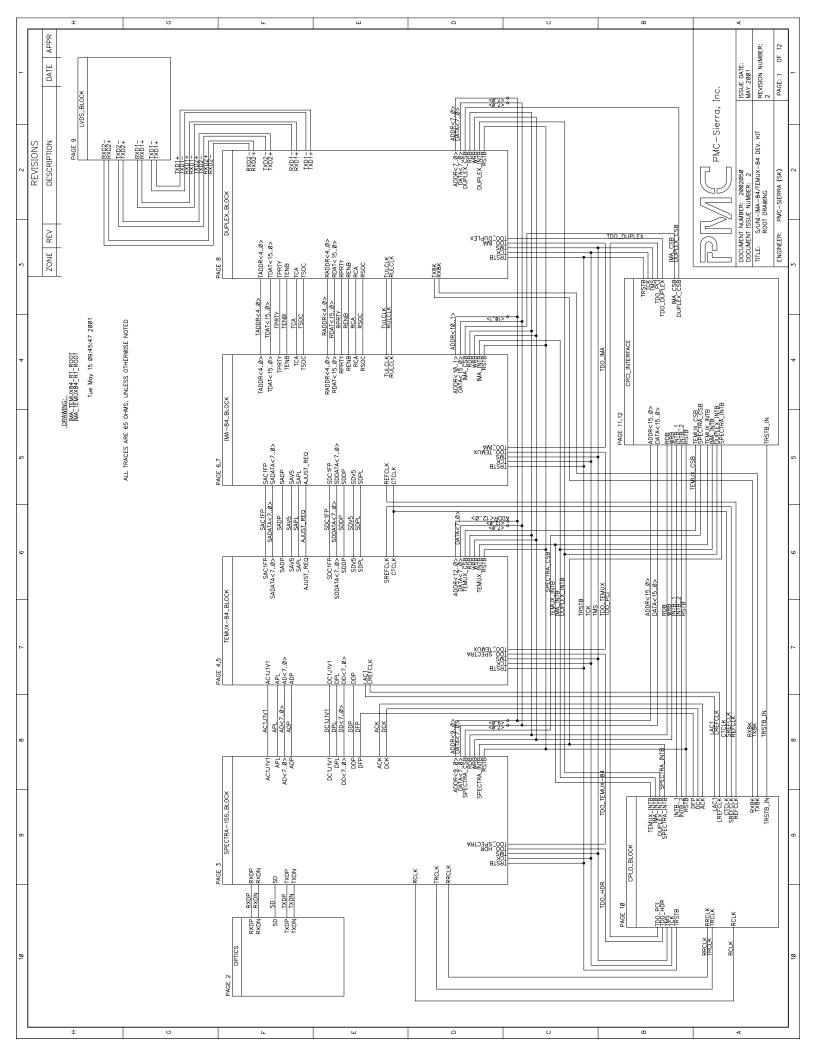

## Figure 8 Block Diagram of S/UNI-IMA-84/ TEMUX-84 Development Kit

PMC-Sierra, Inc.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

### 4 BLOCK DESCRIPTION

The following sections describe the function of each hardware block shown in Figure 8.

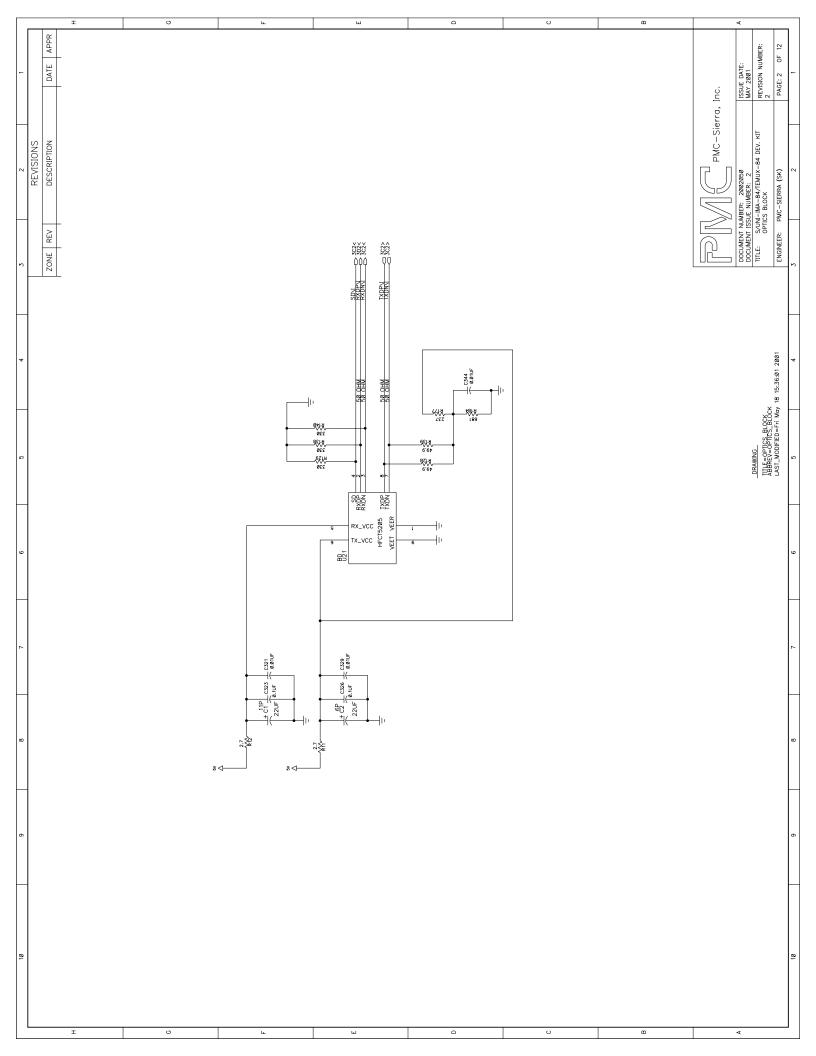

#### 4.1 Optics

Conversion between the optical OC-3 signal and the electrical STS-3 signal is accomplished using the HP HFCT-5905 optical transceiver.

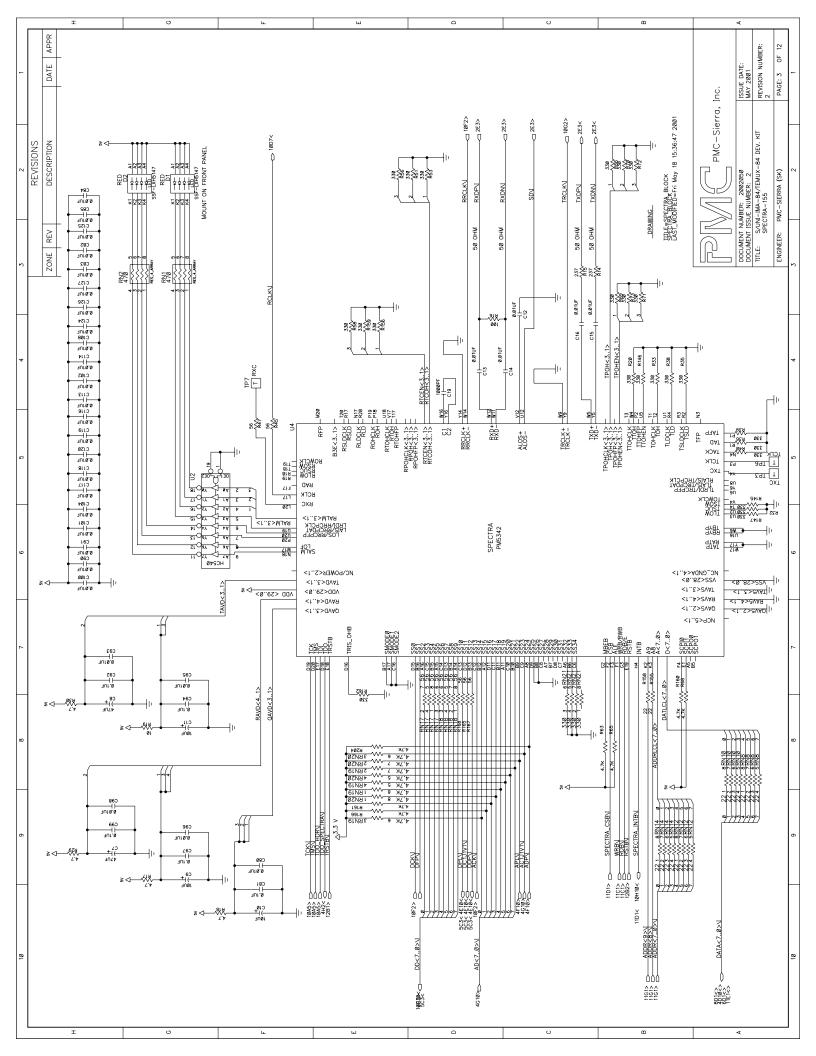

#### 4.2 PM5342 SPECTRA-155

The PM5342 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER (SPECTRA-155) terminates the transport and path overhead of STS-1 (STM-0/AU3) and STS-3/3c (STM-1/AU3/AU4) streams at 51.84 Mbit/s and 155.52 Mbit/s respectively. The SPECTRA-155 implements significant functions for a SONET/SDH compliant line interface.

The SPECTRA-155 is implemented in low power, +5 Volt, CMOS technology. It has TTL and pseudo ECL (PECL) compatible inputs and outputs and is packaged in a 256-pin SBGA package.

#### 4.3 PM8316 TEMUX-84

The TEMUX-84 is a high density T1/E1 framer with integrated VT/TU Mappers and M13 Multiplexers. PM8316 provides framing and multiplexing for 84 T1 channels or 63 E1 channels into three channelized DS-3's or alternatively maps the T1/E1 channels directly into a SONET/SDH OC-3.

The TEMUX-84 is configured for a Telecom Bus Line Side Interface, and a Scaleable Bandwidth Interconnect (SBI) Bus System Side Interface. The Telecom bus is used to transfer SONET Synchronous Payload Envelopes (SPE) between the SPECTRA-155 and the TEMUX-84. The SBI bus is used to interface to a link layer device, in this case the S/UNI-IMA-84.

#### 4.4 PM7341 S/UNI-IMA-84

The PM7341 S/UNI-IMA-84 is a monolithic integrated circuit that implements the Inverse Multiplexing for ATM protocol over up to 84 T1 links or 63 E1 links when using the high density SBI interface or 32 independent T1/E1 links using the clock and data interface. The S/UNI-IMA-84 can support up to 42 simultaneous IMA groups and each IMA group can support 1 to 32 links with a maximum of 84 links in total. Each group can consist of either T1 or E1 links. Alternatively, the

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

S/UNI-IMA-84 can be used for cell delineation of up to 84 T1 links, 63 E1 links or 3 DS3 links.

### 4.4.1 SDRAM

Two configurations of external SDRAM are supported, 16Mbit (1Mbit x 16) and 64 Mbit (4Mbit x 16), both of which are single chip devices.

## 4.5 PM7350 S/UNI-DUPLEX

The PM7350 S/UNI-DUPLEX is a monolithic integrated circuit, typically used with its sister device, the S/UNI-VORTEX, to implement a point-to-point serial backplane interconnect architecture. The primary role of the S/UNI-DUPLEX is to interface to up to 32 devices (typically framers or PHYs) and transfer 52-56 byte data cells in serial format to/from a backplane. Devices interface to the S/UNI-DUPLEX via an 8 or 16-bit SCI-PHY/UTOPIA/Any-PHY bus, or optionally via a 16-port clock and data interface.

Each S/UNI-DUPLEX can connect to two 100 to 200 Mb/s Low Voltage Differential Signal (LVDS) serial links. A microprocessor port provides access to internal configuration and monitoring registers. The microprocessor port may also be used to insert and extract cells in support of an embedded microprocessor communication channel.

#### 4.6 Bus Interfaces

#### 4.6.1 Telecom Bus Interface

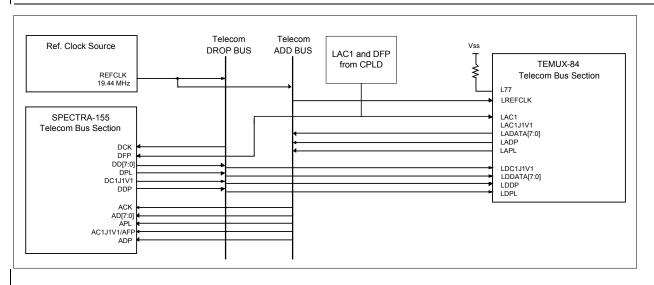

The Telecom bus is used to transfer SONET Synchronous Payload Envelopes (SPE) between the SPECTRA-155 and the TEMUX-84 devices. The connectivity is as shown in Figure 9.

REFERENCE DESIGN PMC - 2002050

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

#### Figure 9 Telecom Bus Interface

In the receive direction, the SONET Payload is presented to the Telecom DROP bus to be received by the TEMUX-84. The TEMUX-84 will terminate the SONET Payload, demultiplex and remap the VT1.5 data into T1 data that will be sent to the S/UNI-IMA-84.

In the transmit direction, the TEMUX-84 drives the Telecom ADD bus. The transmitted SPE is then received and processed by the SPECTRA-155 device.

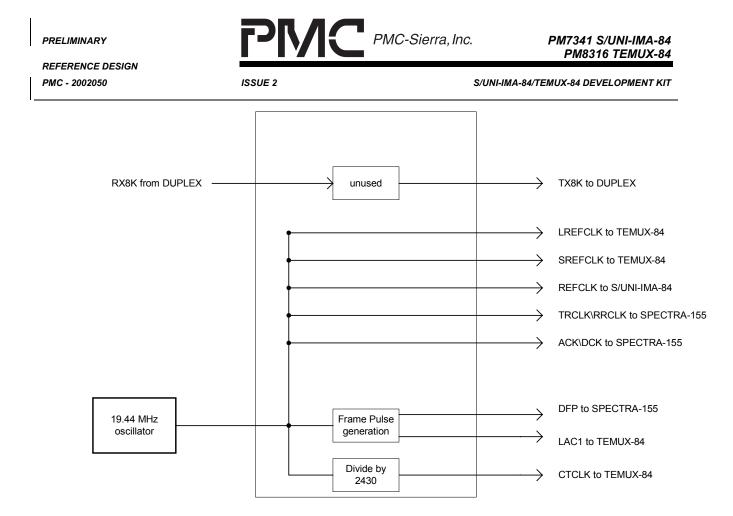

The TEMUX-84 utilizes the LAC1 signal to identify the frame and multiframe boundaries on the Add data bus. The signal is generated in the CPLD by dividing a 19.44 MHz clock by 9720. The SPECTRA-155 (DFP) also uses this frame pulse.

PMC-Sierra, Inc.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## 4.6.2 SBI Bus Interface

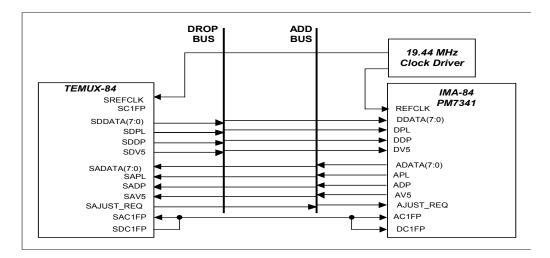

The TEMUX-84 device features a Scaleable Bandwidth Interconnect (SBI) bus to interface to link layer devices like the S/UNI-IMA-84. The SBI bus connectivity between TEMUX-84 and the S/UNI-IMA-84 is shown in Figure 10.

## Figure 10 SBI Bus Interface

In the receive direction, the TEMUX-84 will transmit a SPE composed of T1/E1's or DS3's to the S/UNI-IMA-84 via the SBI DROP bus.

In the transmit direction, the S/UNI-IMA-84 will transmit SPE's to the TEMUX-84 device via the SBI ADD Bus.

The SBI bus utilizes the C1FP signal to indicate SBI Bus multiframe alignment, which occurs every 500  $\mu$ s. The signal is provided by the TEMUX-84.

## 4.6.3 UTOPIA Level 2 Bus Interface

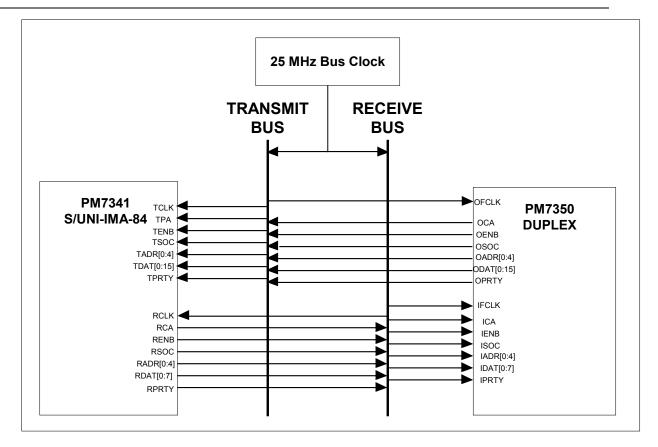

The UTOPIA Level 2 bus is used to transfer ATM cells between the S/UNI-IMA-84 and the S/UNI-DUPLEX. The S/UNI-DUPLEX serves as the bus master and continuously polls the S/UNI-IMA-84 for transmit (receive) data. Note that for this kit, the UTOPIA Level 2 bus shall run on an external 25 MHz oscillator; however the S/UNI-DUPLEX and the S/UNI-IMA-84 can support a maximum UL2 bus rate of 52 MHz. The UTOPIA L2 interface is software selectable to be 8 or 16 bits wide. This kit is designed for a 16-bit wide UTOPIA L2 bus. The architecture is as shown in Figure 11.

PMC - 2002050

REFERENCE DESIGN

PMC-Sierra, Inc.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## Figure 11 UTOPIA Level 2 Bus Interface

## 4.7 CompactPCI Bridge

The S/UNI-IMA-84/TEMUX-84 Development Kit does not have an onboard microprocessor and so the PCI bus host processor card interfaces with this development kit via a CPCI bridge device, which only utilizes a read/write (non-burst) register sequence and interrupt service.

The hot swap compatible PLX PCI 9030 (PCI 9030) Bus Target is employed as the CPCI bus interface.

The PCI 9030 has a 32 long word (lword) write FIFO and 16 lword read FIFO allowing the CPCI bus to burst data to and from the external microprocessor and the PMC-Sierra devices. The Local bus interface of the PCI 9030 is generic and very flexible, supporting 8, 16, and 32-bit transfers operating in multiplexed or non-multiplexed modes as big or little endian at a clock rate asynchronous to the PCI bus up to 60MHz. The Local bus is partitioned into 4 distinct user-definable address spaces that can be configured independently. Each Local address

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

space can be configured to optionally support burst mode transfers and prefetching. The timing of each address space is specifiable via a set of programmable wait states as well as supporting a ready signal used to insert additional wait states.

In this development kit, the host processor will access the Local devices via the PCI 9030 CPCI Bridge configured in non-multiplexed 16-bit address and 16-bit data bus mode. The Local bus is clocked at 33MHz by looping the buffered PCI clock output (BCLKO) available from the PCI 9030 back to the Local bus clock input.

The PCI 9030 is designed to operate with either a 33 or 66 MHz PCI bus in a +3.3 V signaling environment, but is also +5 V tolerant on its PCI interface.

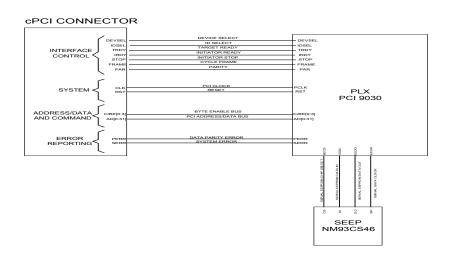

## 4.8 SEEP

The NM93CS56 Serial EEPROM from Fairchild Semiconductor is used to store configuration information for the PCI 9030 Bridge. This specific SEEP (or equivalent) is required by PCI 9030 because it supports sequential read operations.

The SEEP is 1Kbit deep, 256 bits of which are occupied by the PCI 9030 configuration data, leaving 768 bits unused. The SEEP clock is 250 kHz, which is derived from the PCI clock of 33 MHz internally divided by 132.

#### 4.8.1 Card ID Number

The Applications specific Card number is stored in the serial EEPROM. The Card ID assignment is shown in Table 1 below.

| Device                   | Vendor ID | Device ID | Subsystem<br>Vendor ID | Subsystem ID                                                     |

|--------------------------|-----------|-----------|------------------------|------------------------------------------------------------------|

| Unconfigured<br>PCI 9030 | 10B5h     | 9030h     | 11F8h (PMC-<br>Sierra) | 2356h<br>S/UNI-IMA-<br>84/TEMUX-84<br>Development kit<br>Issue 1 |

#### Table 1 PCI Card ID Codes

The 11F8 hex is PMC-Sierra's registered vendor ID. Subsystem ID 2356 hex is unregistered ID for the S/UNI-IMA-84/TEMUX-84 Development kit Issue 1.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

#### 4.8.2 Serial EEPROM Load Registers

The PCI 9030 can be initialized to a large extent by reading data from its serial EEPROM port during initialization. Reading the data from the serial EEPROM is equivalent to directly writing to the 9030's configuration registers via the CPU.

The S/UNI-IMA-84/TEMUX-84 Development kit includes an EEPROM for this purpose. Table 2 illustrates the **preliminary** serial EEPROM Load Registers' contents.

Refer to the PCI 9030 datasheet for detailed information on the format of the configuration data stored in the SEEP.

| SEEP<br>Offset | Description                                                                         | PCI 9030 Register Bits<br>Affected | Setting |

|----------------|-------------------------------------------------------------------------------------|------------------------------------|---------|

| 0h             | Device ID                                                                           | PCIIDR[31:16]                      | 9030h   |

| 2h             | Vendor ID                                                                           | PCIIDR[15:0]                       | 10B5h   |

| 4h             | PCI Status                                                                          | PCISR[15:0]                        | 0290h   |

| 6h             | PCI Command                                                                         | PCIICR[                            | 0000h   |

| Ah             | Class Code                                                                          | PCICCR[23:8]                       | 0001h   |

| 8h             | Class Code / Revision                                                               | PCICCR[7:0] / PCIREV[7:0]          | 0680h   |

| Ch             | Subsystem ID                                                                        | PCISID[15:0]                       | 2356h   |

| Eh             | Subsystem Vendor ID                                                                 | PCISVID[15:0]                      | 11F8h   |

| 10h            | MSW New Capability Pointer                                                          | Reserved                           | XXXXh   |

| 12h            | LSW New Capability Pointer                                                          | CAP_PTR[7:0]                       | XX40h   |

| 14h            | (Maximum Latency and Minimum Grant are not loadable)                                | Reserved                           | XXXXh   |

| 16h            | Interrupt Pin (Interrupt Line Routing is not loadable)                              | PCIIPR[7:0] / PCIILR[7:0]          | 0100h   |

| 18h            | MSW of Power Management Capabilities                                                | PMC[14:11, 5, 3:0]                 | 4801h   |

| 1Ah            | LSW of Power Management Next Capability Pointer /<br>Power Management Capability ID | PMNEXT[7:0] / PMCAPID[7:0]         | 4801h   |

| 1Ch            | MSW of Power Management Data / PMCSR Bridge<br>Support Extension                    | Reserved                           | XXXXh   |

| 1Eh            | LSW of Power Management Control / Status                                            | PMCSR[14:8]                        | 0000h   |

| 20h            | MSW of Hot Swap Control / Status                                                    | Reserved                           | XXXXh   |

| 22h            | LSW of Hot Swap Next Capability Pointer / Hot Swap<br>Control                       | HS_NEXT[7:0] / HS_CNTL[7:0]        | 4C06h   |

| 24h            | PCI Vital Product Data Address                                                      | Reserved                           | 0000h   |

#### Table 2 PCI 9030 Serial EPROM Load Registers

PMC - 2002050

REFERENCE DESIGN

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

| SEEP<br>Offset | Description                                                                   | PCI 9030 Register Bits<br>Affected | Setting |

|----------------|-------------------------------------------------------------------------------|------------------------------------|---------|

| 26h            | PCI Vital Product Next Capability Pointer / PCI Vital<br>Product Data Control | PVPD_NEXT[7:0] /<br>PVPDCNTL[7:0]  | 0003h   |

| 28h            | MSW of Range for PCI-to-Local Address Space 0                                 | LAS0RR[31:16]                      | 0FF0h   |

| 2Ah            | LSW of Range for PCI-to-Local Address Space 0                                 | LAS0RR[15:0]                       | 0000h   |

| 2Ch            | MSW of Range for PCI-to-Local Address Space 1                                 | LAS1RR[31:16]                      | 0000h   |

| 2Eh            | LSW of Range for PCI-to-Local Address Space 1                                 | LAS1RR[15:0]                       | 0000h   |

| 30h            | MSW of Range for PCI-to-Local Address Space 2                                 | LAS2RR[31:16]                      | 0000h   |

| 32h            | LSW of Range for PCI-to-Local Address Space 2                                 | LAS2RR[15:0]                       | 0000h   |

| 34h            | MSW of Range for PCI-to-Local Address Space 3                                 | LAS3RR[31:16]                      | 0000h   |

| 36h            | LSW of Range for PCI-to-Local Address Space 3                                 | LAS3RR[15:0]                       | 0000h   |

| 38h            | MSW of Range for PCI-to-Local Expansion ROM                                   | EROMRR[31:16]                      | FFFFh   |

| 3Ah            | LSW of Range for PCI-to-Local Expansion ROM                                   | EROMRR[15:0]                       | 0000h   |

| 3Ch            | MSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 0         | LAS0BA[31:16]                      | 0000h   |

| 3Eh            | LSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 0         | LAS0BA[15:0]                       | 0001h   |

| 40h            | MSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 1         | LAS1BA[31:16]                      | 0000h   |

| 42h            | LSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 1         | LAS1BA[15:0]                       | 0000h   |

| 44h            | MSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 2         | LAS2BA[31:16]                      | 0000h   |

| 46h            | LSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 2         | LAS2BA[15:0]                       | 0000h   |

| 48h            | MSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 3         | LAS3BA[31:16]                      | 0000h   |

| 4Ah            | LSW of Local Base Address (Remap) for PCI-to-Local<br>Address Space 3         | LAS3BA[15:0]                       | 0000h   |

| 4Ch            | MSW of Local Base Address (Remap) for Expansion ROM                           | EROMBA[31:16]                      | 0010h   |

| 4Eh            | LSW of Local Base Address (Remap) for Expansion ROM                           | EROMBA[15:0]                       | 0000h   |

| 50h            | MSW of Bus Region Descriptors for Local Address Space<br>0                    | LAS0BRD1[31:16]                    | 5481h   |

| 52h            | LSW of Bus Region Descriptors for Local Address Space<br>0                    | LAS0BRD1[15:0]                     | 0080h   |

PMC - 2002050

REFERENCE DESIGN

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

| SEEP<br>Offset | Description                                                                                | PCI 9030 Register Bits<br>Affected                        | Setting |

|----------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------|

| 54h            | MSW of Bus Region Descriptors for Local Address Space<br>1                                 | LAS1BRD1[31:16]                                           | 0000h   |

| 56h            | LSW of Bus Region Descriptors for Local Address Space 1                                    | LAS1BRD1[15:0]                                            | 0000h   |

| 58h            | MSW of Bus Region Descriptors for Local Address Space 2                                    | LAS2BRD1[31:16]                                           | 0000h   |

| 5Ah            | LSW of Bus Region Descriptors for Local Address Space 2                                    | LAS2BRD1[15:0]                                            | 0000h   |

| 5Ch            | MSW of Bus Region Descriptors for Local Address Space 3                                    | LAS3BRD1[31:16]                                           | 0000h   |

| 5Eh            | LSW of Bus Region Descriptors for Local Address Space 3                                    | LAS3BRD1[15:0]                                            | 0000h   |

| 60h            | MSW of Bus Region Descriptors for Expansion ROM                                            | EROMBRD[31:16]                                            | 0000h   |

| 62h            | LSW of Bus Region Descriptors for Expansion ROM                                            | EROMBRD[15:0]                                             | 0000h   |

| 64h            | MSW of Chip Select (CS) 0 Base and Range                                                   | CS0BASE[31:16]                                            | 0002h   |

| 66h            | LSW of Chip Select (CS) 0 Base and Range                                                   | CS0BASE[15:0]                                             | 0001h   |

| 68h            | MSW of Chip Select (CS) 1 Base and Range                                                   | CS1BASE[31:16]                                            | 0006h   |

| 6Ah            | LSW of Chip Select (CS) 1 Base and Range                                                   | CS1BASE[15:0]                                             | 0001h   |

| 6Ch            | MSW of Chip Select (CS) 2 Base and Range                                                   | CS2BASE[31:16]                                            | 000Ah   |

| 6Eh            | LSW of Chip Select (CS) 2 Base and Range                                                   | CS2BASE[15:0]                                             | 0001h   |

| 70h            | MSW of Chip Select (CS) 3 Base and Range                                                   | CS3BASE[31:16]                                            | 000Eh   |

| 72h            | LSW of Chip Select (CS) 3 Base and Range                                                   | CS3BASE[15:0]                                             | 0001h   |

| 74h            | Serial EEPROM Write-Protected Address Boundary                                             | PROT_AREA[7:0]                                            | 0030h   |

| 76h            | LSW of Interrupt Control / Status Register                                                 | INTCSR[15:0]                                              | 0000h   |

| 78h            | MSW of PCI Target Response, Serial EEPROM, and<br>Initialization Control                   | CNTRL[31:16]                                              | 0078h   |

| 7Ah            | LSW of PCI Target Response, Serial EEPROM, and<br>Initialization Control                   | CNTRL[15:0]                                               | 0000h   |

| 7Ch            | MSW of General Purpose I/O Control                                                         | GPIOC[31:16]                                              | 0000h   |

| 7Eh            | LSW of General Purpose I/O Control                                                         | GPIOC[15:0]                                               | 0240h   |

| 80h            | MSW of Hidden Power Management Data Select (refer to Section 7.2.1 of PCI 9030 Data sheet) | PMDATA[7:0] hidden, $D_0$ and $D_{3hot}$ Power Dissipated | 0000h   |

| 82h            | LSW of Hidden Power Management Data Select (refer to Section 7.2.1 of PCI 9030 Data sheet) | PMDATA[7:0] hidden, $D_0$ and $D_{3hot}$ Power Consumed   | 0000h   |

PMC - 2002050

**REFERENCE DESIGN**

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

| SEEP<br>Offset | Description                                                                               | PCI 9030 Register Bits<br>Affected                     | Setting |

|----------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|---------|

| 84h            | MSW of Hidden Power Management Data Scale (refer to Section 7.2.1 of PCI 9030 Data Sheet) | Reserved                                               | 0000h   |

| 86h            | LSW of Hidden Power Management Data Scale (refer to Section 7.2.1 of PCI 9030 Data Sheet) | PMCSR[14:13] hidden, Bits[7:0]<br>are used as follows: | 0000h   |

|                |                                                                                           | [7:6] D <sub>3hot</sub> Power Dissipated               |         |

|                |                                                                                           | [5:4] D <sub>0</sub> Power Dissipated                  |         |

|                |                                                                                           | [3:2] D <sub>3hot</sub> Power Consumed                 |         |

|                |                                                                                           | [1:0] D <sub>0</sub> Power Consumed                    |         |

| 87-            | Blank                                                                                     |                                                        |         |

| 100h           |                                                                                           |                                                        |         |

#### 4.9 CPLD

A Xilinx XC9536XL CPLD provides the miscellaneous logic required for the board, and framing pulses that is required by the SPECTRA-155 as shown in Figure 12. The timing requirements for the design were such to allow the slowest speed grade of XC9536XL available (-10) to be used. Faster pin-compatible devices are available should future requirements have tighter timing constraints. Pin compatible devices with more internal logic resources are also available. The logic for the CPLD is specified exclusively in a single VHDL source file. The VHDL code is available in APPENDIX D: VHDL Code for CPLD. 16 of the 34 I/O pins available are used. 14 of the remaining I/O pins are accessible via headers.

The CPLD is programmed via its JTAG port. The JTAG port is accessible through the debug header. This interface allows for the possibility of remote upgrades of the CPLD configuration.

# Figure 12 CPLD Logic Block Diagram

## 4.9.1 Local Bus Glue Logic

Some additional logic is required to glue the interrupt bits from the four PMC-Sierra devices to the PCI bridge Local bus. The four interrupts from devices are decoded to two interrupt bits to the PCI bridge. All four interrupt bits are also sent to General Purpose I/O pins of the PCI bridge.

## 4.10 Full Hot Swap Capability

Hot swap functionality allows the orderly insertion and removal of boards without adversely affecting system operation. The S/UNI-IMA-84/TEMUX-84 development kit is a Full Hot Swap board. Full Hot Swap boards have the minimum Hot Swap features plus the additional resources for software connection control. The following Full Hot Swap resources are provided to software executing on the external microprocessor:

• An ENUM# signal, which is an open collector (open drain) bussed signal, to signal a change in status for the board.

| PRE | LIMII | VARY |

|-----|-------|------|

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

- A switch, actuated with the lower ejector handle, indicates the beginning of the extraction process or end of the insertion process.

- An LED to indicate the status of the software connection process.

- A set of four control and status bits on each board which allows the system host's software to determine the source of the ENUM# signal and control the LED.

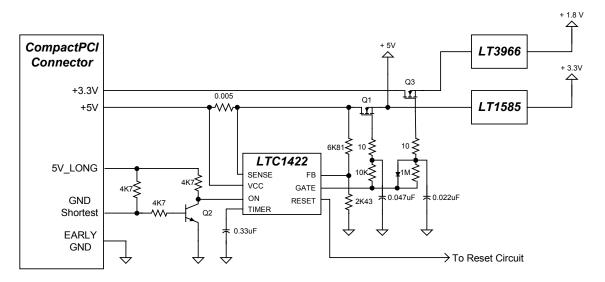

This development kit employs a hot swap compatible CPCI bridge, PCI 9030, and a hot swap controller, the Linear Technology LTC1422. The CPCI connector is assembled with three different length pins, as required by the hot swap specification [PICMG 2.1 R1.0]. Supporting circuitry is also carefully designed to not impair the hot swap ability.

Please refer to the PCI 9030 data sheet and the CompactPCI® Hot Swap Specification, R1.0 for further details regarding these resources.

# 4.10.1 Power Supply with Hot Swap Controller

The power supply for the S/UNI-IMA-84/TEMUX-84 Development Kit is as shown in Figure 13. Integral to the circuit is the use of the LTC1422 Hot Swap Controller.

# Figure 13 Power Supply with integrated hot swap circuitry

The S/UNI-IMA-84/TEMUX-84 Development Kit contains components that operate at 1.8V, 3.3V and 5V, referenced to ground. The 5V supply is provided

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

to the board through the CompactPCI connector. The 1.8V and 3.3V supplies are generated on the board via DC-DC voltage regulators.

It is required that 5V power is provided before both 1.8V and 3.3V power to avoid device latchup. Please refer to the respective data sheets of each device for further details regarding device power-up.

The first mating pins are 5V\_LONG and Early GND. When these pins initially mate, Q2 saturates and the ON pin of the LTC1422 is held low. The LT1422 has yet to receive power, which keeps both MOSFETs open (off).

When the shortest pins mate with the backplane, GND\_Shortest connecting to the base of Q2 causes Q2 to turn off and the ON pin then becomes logic high. The LTC1422 then begins to slowly ramp up the gate voltage for Q1 & Q3, causing the MOSFETS to gradually turn on, limiting the inrush current to the board to a safe level. This, in turn, causes the gate voltages on Q1 and Q3 to rise, turning the transistors on. Because the resistor and capacitor network used for Q3 is different than Q1, Q3 powers up with a 20 ms delay.

Once Q1 and Q3 turn on, the LP3966 is used to generate the +1.8V supply from the CompactPCI +3.3V line, while the LT1585 generates +3.3V from the CompactPCI +5V line. The board +5V supply is generated directly from the CompactPCI +5V line. The LP3966 is capable of supplying 3A, while the LT1585 can supply 4.6A.

Should the voltage across the 0.005  $\Omega$  resistor exceed 50 mV for more than 10  $\mu$ s, an internal circuit breaker will trip, pulling the GATE output voltage to ground.

#### 4.10.2 Ejector Handle and LED

The ejector handle has a built-in microswitch, which toggles when the ejector changes position. A blue LED signals the card's readiness for removal. When the ejector handle switch is opened the PCI9030 asserts *ENUM*# to inform the host CPU that the card is about to be removed. When the blue LED is turned on, the card may be safely removed.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

## 4.11 CPCI Bridge Hardware Interfaces

#### 4.11.1 CPCI System Bus Interface

The host processor located on an external board will access the PMC-Sierra devices located on-board through a CPCI connector. The serial EEPROM (SEEP) is used to store configuration information for the PCI 9030 bridge.

The system bus interface is a straightforward pin-to-pin connection between both the CPCI connector to the PCI 9030 and the SEEP to the PCI 9030. The system bus pins consist of interface control, address/data control and error reporting. For further functional description of each pin, please refer to any standard book covering PCI technology as well as the PCI 9030 and SEEP datasheet.

## Figure 14 CPCI System Bus Interface Block Diagram

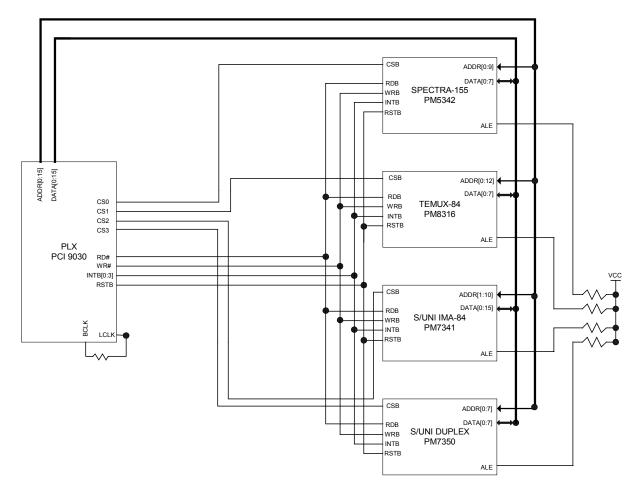

#### 4.11.2 PCI 9030-Local Bus Interface

The PCI 9030 serves as a master device on the Local bus. Upon control from the external processor on the System side bus, the PCI 9030 sends the address and data out to the Local bus, while its control information is sent to the CPLD, which handles all decode logic and timing requirements for each PMC-Sierra device.

The PCI 9030 is configured to operate the Local Bus in non-multiplexed mode. Access to each PMC-Sierra device by the PCI 9030 is very similar in operation, with the difference between each access being the number of address and data

REFERENCE DESIGN PMC - 2002050

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

interface pins that each PMC-Sierra device microprocessor block contains, and the set-up and hold timing parameters.

## Figure 15 PCI 9030 Local Bus Interface Block Diagram

с. РМ734 РМ3

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

## 4.12 Oscillators

A 19.44 MHz  $\pm$  20ppm oscillator is required on the card to drive the Telecom bus and SBI bus. The CPLD will use this clock source to generate the 2 kHz synchronization pulse and other framing pulses.

A 37.056 MHz  $\pm$  32ppm oscillator is required on the card to drive the digital phase locked loop on the TEMUX-84 that performs jitter attenuation on the T1 recovered clocks.

A 49.152 MHz  $\pm$  32ppm oscillator is required on the card to drive the digital phase locked loop on the TEMUX-84 that performs jitter attenuation on the E1 recovered clocks.

A 51.84 oscillator is required on the card to generate a gapped DS3 clock for the TEMUX-84.

A 55 MHz oscillator is required on the card to drive the system clock of the S/UNI-IMA-84 for use with the external SDRAM device.

A 25 MHz oscillator is required on the card to drive the UTOPIA Level 2 bus.

PM7341 S/UNI-IMA-84 PM8316 TEMUX-84

ISSUE 2

## 5 ANALYSIS

#### 5.1 INTERFACE TIMING

In the timing analysis figures of the section, a gray waveform indicates uncertainty, and a black waveform indicates an input that is not valid since more than one device may be driving the signal at that time. All times are measured in nanoseconds (ns).

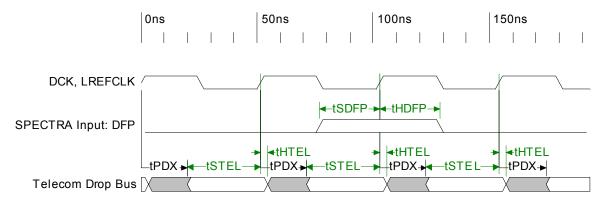

## 5.1.1 SPECTRA-155 – TEMUX-84 Telecom DROP Bus

The Telecom DROP Bus is the ingress interface between SPECTRA-155 data and control outputs and TEMUX-84 data and control inputs. On the DROP bus, DCK provides timing to the SPECTRA-155 and LREFCLK provides timing to the TEMUX-84. These clocks need to be synchronized for correct operation of the bus. The Telecom bus is synchronized to a 19.44 MHz clock source. The AC1J1V1 signal is sampled on the rising edge of LREFCLK and indicates frame, payload and tributary multiframe boundaries. See Figure 16 below for a diagram of the Telecom drop bus timing.

## Figure 16 Telecom DROP Bus Timing Diagram

In reference to Figure 16, the sequence of events for one Telecom DROP bus clock cycle is as follows:

- 1. The SPECTRA-155 updates DD[7:0], DDP, DPL, and DC1J1V1 on the rising edge of DCK after a propagation delay, tP Dx.

- 2. On the next rising edge, the TEMUX-84 samples LDDATA[7:0], LDDP, LDPL, and LDC1J1V1 on the rising edge of LREFCLK. The TEMUX-84 inputs require a set-up time of tS TEL and a hold time of tH TEL relative to the rising edge of LREFCLK.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

3. On the same rising edge of DCK, the SPECTRA-155 samples DFP. DFP requires a set-up time of tS DFP and a hold time of tH DFP.

The output propagation delays involved in Figure 16 are shown in the following table:

## Table 3 Telecom Drop Bus Propagation Delays

| Name  | Device   | Description          | Min | Max |

|-------|----------|----------------------|-----|-----|

| tP DX | SPECTRA- | DCK High to Dx Valid | 3   | 20  |

|       | 155      |                      |     |     |

The input constraints involved in Figure 16 are shown in the following table:

## **Table 4 Telecom Drop Bus Timing Constraints**

| Name   | Device          | Description             | Min | Actual | Margin |

|--------|-----------------|-------------------------|-----|--------|--------|

| tS DFP | SPECTRA-<br>155 | DFP Set-up Time         | 5   | 25.72  | 20.72  |

| tH DFP | SPECTRA-<br>155 | DFP Hold Time           | 1   | 25.72  | 24.72  |

| tS TEL | TEMUX-84        | Telecom Bus Set-up Time | 5   | 31.44  | 26.44  |

| tH TEL | TEMUX-84        | Telecom Bus Hold Time   | 1   | 3      | 2      |

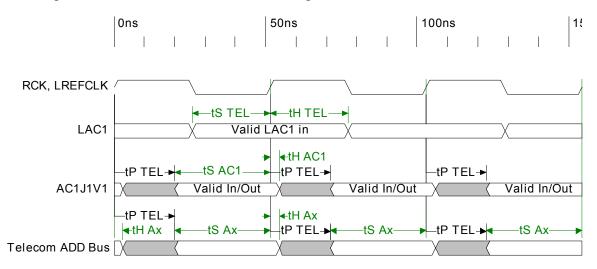

## 5.1.2 SPECTRA-155 – TEMUX-84 Telecom ADD Bus

The Telecom ADD Bus is the egress interface between SPECTRA data and control inputs and TEMUX data and control outputs. See Figure 17 below for a diagram of the Telecom ADD bus timing.

ISSUE 2

#### Figure 17 Telecom ADD Bus Timing Diagram

In reference to Figure 17, the sequence of events for one Telecom ADD bus clock cycle is as follows:

- 1. The TEMUX-84 updates LADATA[7:0], LADP, and LAPL on the falling edge of LREFCLK after a propagation delay, tP TEL.

- 2. On the next rising edge, SPECTRA samples AD[7:0], ADP, and APL on the rising edge of ACK. These SPECTRA inputs require a set-up time of tS Ax and a hold time of tH Ax relative to the rising edge of ACK.

- 3. On the same rising edge of LREFCLK, the TEMUX-84 samples LAC1. LAC1 requires a set-up time of tS TEL and a hold time of tH TEL.

The output propagation delays involved in Figure 17 are shown in the following table:

| Name     | Device | Description                           | Min | Мах |

|----------|--------|---------------------------------------|-----|-----|

| tP TELOE | TEMUX- | LREFCLK to Tristateable Outputs going | 0   | 13  |

|          | 84     | Valid from Tristate                   |     |     |

| tZ TEL   | TEMUX- | LREFCLK to Tristateable Outputs going | 3   | 20  |

|          | 84     | Tristate                              |     |     |

| tP TEL   | TEMUX- | LREFCLK to Output Valid               | 3   | 20  |

|          | 84     |                                       |     |     |

#### Table 5 Telecom Add Bus Propagation Delays

The input constraints involved in Figure 17 are shown in the following table:

#### **Table 6 Telecom Add Bus Timing Constraints**

| Name   | Device   | Description             | Min | Actual | Margin |

|--------|----------|-------------------------|-----|--------|--------|

| tS TEL | SPECTRA- | Telecom Bus Set-up Time | 5   | 25.72  | 20.72  |

|        | 155      |                         |     |        |        |

| tH TEL | SPECTRA- | Telecom Bus Hold Time   | 1   | 25.72  | 24.72  |

|        | 155      |                         |     |        |        |

| tS Ax  | SPECTRA- | Ax Set-up Time          | 5   | 31.44  | 26.44  |

|        | 155      |                         |     |        |        |

| tH Ax  | SPECTRA- | Ax Hold Time            | 1   | 3      | 2      |

|        | 155      |                         |     |        |        |

| tS AC1 | TEMUX-84 | AC1J1V1 Set-up Time     | 5   | 31.44  | 26.44  |

| tH AC1 | TEMUX-84 | AC1J1V1 Hold Time       | 1   | 3      | 2      |

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

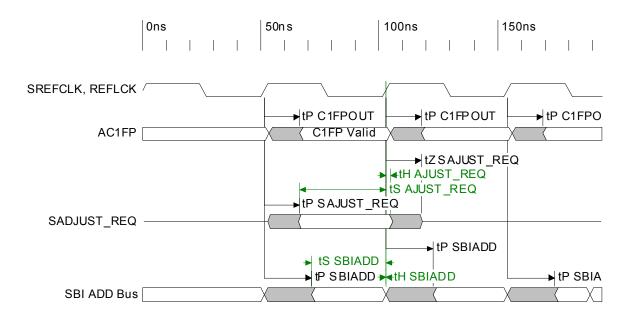

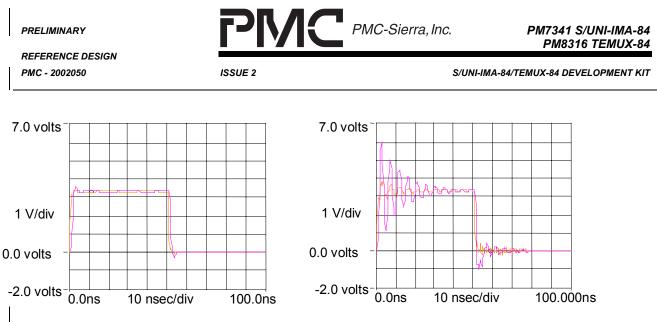

#### 5.1.3 TEMUX-84 – S/UNI-IMA-84 SBI ADD Bus Interface

The SBI ADD Bus is the egress interface between S/UNI-IMA-84 data and control outputs and TEMUX-84 data and control inputs. On the ADD bus, SREFCLK provides timing to the TEMUX-84 and REFCLK provides timing to the S/UNI-IMA-84. These clocks need to be synchronized for correct operation of the bus.

The C1FP frame pulse indicates SBI bus multiframe alignment, which occurs every 500  $\mu$ s. Therefore, this signal is pulsed every 9720 SREFCLKs. In this reference design, C1FP is generated from the SDC1FP pin of the TEMUX-84.

In reference to Figure 18, the S/UNI-IMA-84 outputs are ADATA[7:0], ADP, APL, AC1FP, and AV5. The corresponding TEMUX-84 inputs are SADATA[7:0], SADP, SAPL, SAC1FP, and SAV5. Please see the Pin Description and Functional Timing sections of the device datasheets for the functional description of these signals.

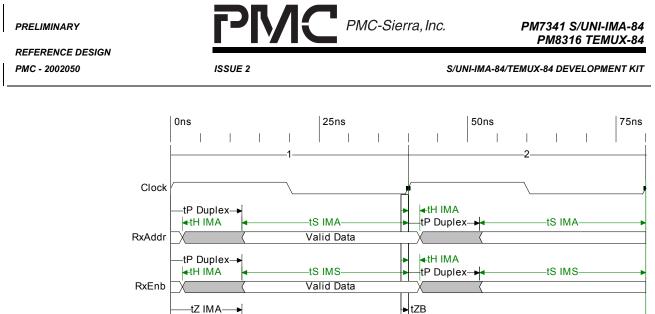

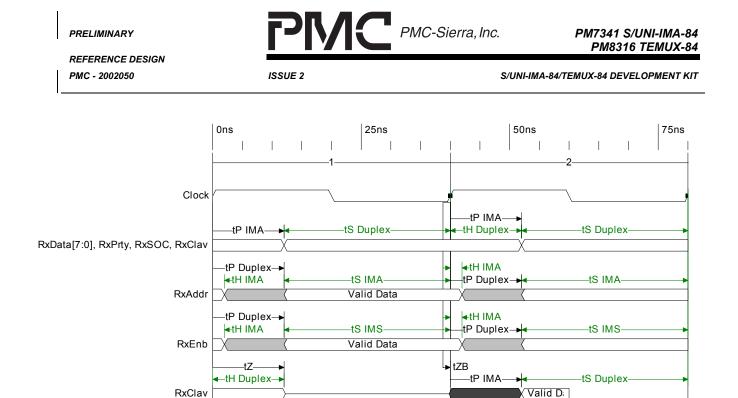

## Figure 18 SBI ADD Bus Timing Analysis

In reference to Figure 18, the sequence of events for one SBI ADD bus clock cycle is as follows:

1. S/UNI-IMA-84 updates ADATA[7:0], ADP, APL, and AV5 on the rising edge of REFCLK after a propagation delay, tP SBIADD.

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

- On the same rising edge, TEMUX-84 updates C1FPOUT after a propagation delay, tP SDC1FP.

- 3. The AJUST\_REQ signal is asserted by the TEMUX-84 to control the data rate of the S/UNI-IMA-84.

- On the next rising edge of SREFCLK, TEMUX-84 samples SADATA[7:0], SADP, SAPL, and SAV5. These TEMUX-84 inputs require a set-up time of tS SBIADD and a hold time of tH SBIADD relative to the rising edge of SREFCLK.

- On the same edge, the S/UNI-IMA-84 samples the SAJUST\_REQ signal. The SAJUST\_REQ signal requires a setup time of tSAJUST and a hold time of tHSAJUST

The output propagation delays involved in Figure 18 are shown in the following table:

# Table 7 SBI Add Bus Propagation Delays

| Name       | Device       | Description                         | Min | Max |

|------------|--------------|-------------------------------------|-----|-----|

| tP SBIADD  | S/UNI-IMA-84 | REFCLK to SBI ADD Bus Outputs Valid | 0   | 20  |

| tP         | TEMUX-84     | SREFCLK to SAJUST_REQ Valid         | 2   | 15  |

| SAJUST_REQ |              |                                     |     |     |

| tZ         | TEMUX-84     | SREFCLK to SAJUST_REQ Tri-state     | 2   | 15  |

| SAJUST_REQ |              |                                     |     |     |

The input constraints involved in Figure 18 are shown in the following table:

# Table 8 SBI Add Bus Timing Constraints

| Name      | Device       | Description                                  | Min | Actual | Margin |

|-----------|--------------|----------------------------------------------|-----|--------|--------|

| tS AJUST  | S/UNI-IMA-84 | SAJUST_REQ Set-up Time to<br>SREFCLK         | 4   | 36.44  | 32.44  |

| tH AJUST  | S/UNI-IMA-84 | SAJUST_REQ Hold Time to<br>SREFCLK           | 0   | 2      | 2      |

| tS SBIADD | TEMUX-84     | SBI ADD Bus Inputs Set-up<br>Time to SREFCLK | 4   | 31.44  | 27.44  |

| tH SBIADD | TEMUX-84     | SBI ADD Bus Inputs Hold<br>Time from SREFCLK | 0   | 0      | 0      |

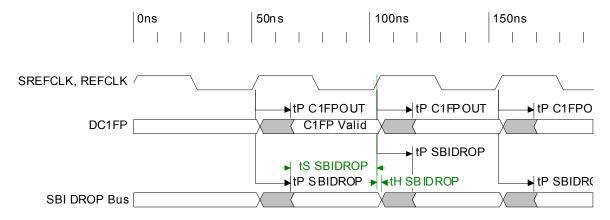

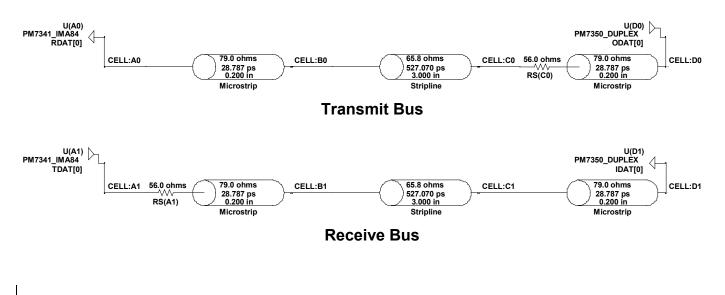

# 5.1.4 TEMUX-84 – S/UNI-IMA-84 SBI DROP Bus Interface

The SBI DROP Bus is the ingress interface between TEMUX-84 data and control outputs and S/UNI-IMA-84 data and control inputs. On the DROP bus, SREFCLK provides timing to the TEMUX-84 and REFCLK provides timing to the

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

S/UNI-IMA-84. These clocks need to be synchronized for correct operation of the bus.

The C1FP frame pulse indicates SBI bus multiframe alignment, which occurs every 500  $\mu$ s. Therefore, this signal is pulsed every 9720 SREFCLKs. In this reference design, C1FP is generated from the SDC1FP pin of the TEMUX-84.

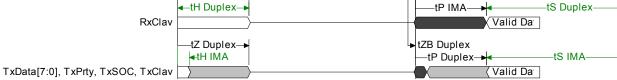

In reference to Figure 19, theTEMUX-84 outputs are SDDATA[7:0], SDDP, SDPL, and SDV5. The corresponding S/UNI-IMA-84 inputs are DDATA[7:0], DDP, DPL, and DV5. Please see the Pin Description and Functional Timing sections of the device datasheets for the functional description of these signals.

# Figure 19 SBI DROP Bus Timing Analysis

In reference to Figure 19, the sequence of events for one SBI DROP bus clock cycle is as follows:

- 1. On the rising edge of REFCLK, TEMUX-84 updates SDDATA[7:0], SDDP, SDPL, and SDV5 after a propagation delay, tP SBIDROP.

- 2. On the same edge, TEMUX-84 updates C1FP after a propagation delay, tP SDC1FP.

- On the next rising edge of SREFCLK, S/UNI-IMA-84 samples DDATA[7:0], DDP, DPL, and DV5. These S/UNI-IMA-84 inputs require a set-up time of tS SBIDROP and a hold time of tH SBIDROP relative to the rising edge of SREFCLK.

The output propagation delays involved in Figure 19 are shown in the following table:

## **Table 9 SBI DROP Bus Propagation Delays**

|  | Name | Device | Description | Min | Max |

|--|------|--------|-------------|-----|-----|

|--|------|--------|-------------|-----|-----|

PMC - 2002050

REFERENCE DESIGN

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

| Name       | Device   | Description                          | Min | Max |

|------------|----------|--------------------------------------|-----|-----|

| tP SBIDROP | TEMUX-84 | REFCLK to SBI DROP Bus Outputs Valid | 0   | 20  |

| tP SDC1FP  | TEMUX-84 | SREFCLK to C1FP Valid                | 2   | 15  |

The input constraints involved in Figure 19 are shown in the following table:

PMC - 2002050

REFERENCE DESIGN

ISSUE 2

S/UNI-IMA-84/TEMUX-84 DEVELOPMENT KIT

| Name       | Device | Description                   | Min | Actual | Margin |

|------------|--------|-------------------------------|-----|--------|--------|

| tS SBIDROP | S/UNI- | SBI DROP Bus Inputs Set-up    | 4   | 31.44  | 27.44  |

|            | IMA-84 | Time to SREFCLK               |     |        |        |

| tH SBIDROP | S/UNI- | SBI DROP Bus Inputs Hold Time | 0   | 0      | 0      |

|            | IMA-84 | from SREFCLK                  |     |        |        |

#### **Table 10 SBI DROP Bus Timing Constraints**

#### 5.1.5 S/UNI-IMA-84 – S/UNI-DUPLEX UTOPIA Level 2 TRANSMIT Bus Interface